【導讀】在電信工業(yè)和微波電路設計領(lǐng)域,普遍使用MOS管控制沖擊電流的方達到電流緩啟動(dòng)的目的。MOS管有導通阻抗Rds_on低和驅動(dòng)簡(jiǎn)單的特點(diǎn),在周?chē)由仙倭吭骷涂梢詷嫵删徛龁?dòng)電路。雖然電路比較簡(jiǎn)單,但只有吃透MOS管的相關(guān)開(kāi)關(guān)特性后才能對這個(gè)電路有深入的理解。

本文首先從MOSFET的開(kāi)通過(guò)程進(jìn)行敘述:

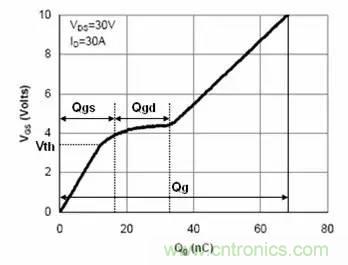

盡管MOSFET在開(kāi)關(guān)電源、電機控制等一些電子系統中得到廣泛的應用,但是許多電子工程師并沒(méi)有十分清楚的理解MOSFET開(kāi)關(guān)過(guò)程,以及MOSFET在開(kāi)關(guān)過(guò)程中所處的狀態(tài)一般來(lái)說(shuō),電子工程師通?;跂艠O電荷理解MOSFET的開(kāi)通的過(guò)程,如圖1所示此圖在MOSFET數據表中可以查到

圖1 AOT460柵極電荷特性

MOSFET的D和S極加電壓為VDD,當驅動(dòng)開(kāi)通脈沖加到MOSFET的G和S極時(shí),輸入電容Ciss充電,G和S極電壓Vgs線(xiàn)性上升并到達門(mén)檻電壓VGS(th),Vgs上升到VGS(th)之前漏極電流Id≈0A,沒(méi)有漏極電流流過(guò),Vds的電壓保持VDD不變。

當Vgs到達VGS(th)時(shí),漏極開(kāi)始流過(guò)電流Id,然后Vgs繼續上升,Id也逐漸上升,Vds仍然保持VDD當Vgs到達米勒平臺電壓VGS(pl)時(shí),Id也上升到負載電流最大值ID,Vds的電壓開(kāi)始從VDD下降。

米勒平臺期間,Id電流維持ID,Vds電壓不斷降低。

米勒平臺結束時(shí)刻,Id電流仍然維持ID,Vds電壓降低到一個(gè)較低的值米勒平臺結束后,Id電流仍然維持ID,Vds電壓繼續降低,但此時(shí)降低的斜率很小,因此降低的幅度也很小,最后穩定在Vds=Id×Rds(on)因此通??梢哉J為米勒平臺結束后MOSFET基本上已經(jīng)導通。

對于上述的過(guò)程,理解難點(diǎn)在于為什么在米勒平臺區,Vgs的電壓恒定?驅動(dòng)電路仍然對柵極提供驅動(dòng)電流,仍然對柵極電容充電,為什么柵極的電壓不上升?而且柵極電荷特性對于形象的理解MOSFET的開(kāi)通過(guò)程并不直觀(guān)因此,下面將基于漏極導通特性理解MOSFET開(kāi)通過(guò)程。

MOSFET的漏極導通特性與開(kāi)關(guān)過(guò)程。

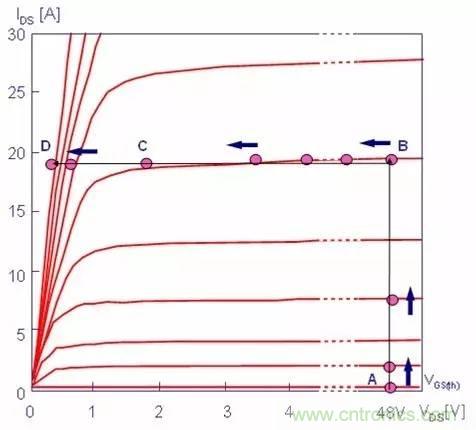

MOSFET的漏極導通特性如圖2所示MOSFET與三極管一樣,當MOSFET應用于放大電路時(shí),通常要使用此曲線(xiàn)研究其放大特性只是三極管使用的基極電流、集電極電流和放大倍數,而MOSFET使用柵極電壓、漏極電流和跨導。

圖2 AOT460的漏極導通特性

三極管有三個(gè)工作區:截止區、放大區和飽和區,MOSFET對應是關(guān)斷區、恒流區和可變電阻區注意:MOSFET恒流區有時(shí)也稱(chēng)飽和區或放大區當驅動(dòng)開(kāi)通脈沖加到MOSFET的G和S極時(shí),Vgs的電壓逐漸升高時(shí),MOSFET的開(kāi)通軌跡A-B-C-D如圖3中的路線(xiàn)所示

圖3 AOT460的開(kāi)通軌跡

開(kāi)通前,MOSFET起始工作點(diǎn)位于圖3的右下角A點(diǎn),AOT460的VDD電壓為48V,Vgs的電壓逐漸升高,Id電流為0,Vgs的電壓達到VGS(th),Id電流從0開(kāi)始逐漸增大

A-B就是Vgs的電壓從VGS(th)增加到VGS(pl)的過(guò)程從A到B點(diǎn)的過(guò)程中,可以非常直觀(guān)的發(fā)現,此過(guò)程工作于MOSFET的恒流區,也就是Vgs電壓和Id電流自動(dòng)找平衡的過(guò)程,即Vgs電壓的變化伴隨著(zhù)Id電流相應的變化,其變化關(guān)系就是MOSFET的跨導:Gfs=Id/Vgs,跨導可以在MOSFET數據表中查到

當Id電流達到負載的最大允許電流ID時(shí),此時(shí)對應的柵級電壓Vgs(pl)=Id/gFS由于此時(shí)Id電流恒定,因此柵極Vgs電壓也恒定不變,見(jiàn)圖3中的B-C,此時(shí)MOSFET處于相對穩定的恒流區,工作于放大器的狀態(tài)

開(kāi)通前,Vgd的電壓為Vgs-Vds,為負壓,進(jìn)入米勒平臺,Vgd的負電壓絕對值不斷下降,過(guò)0后轉為正電壓驅動(dòng)電路的電流絕大部分流過(guò)CGD,以?huà)叱桌针娙莸碾姾?,因此柵極的電壓基本維持不變Vds電壓降低到很低的值后,米勒電容的電荷基本上被掃除,即圖3中的C點(diǎn),于是,柵極的電壓在驅動(dòng)電流的充電下又開(kāi)始升高,如圖3中的C-D,使MOSFET進(jìn)一步完全導通

C-D為可變電阻區,相應的Vgs電壓對應著(zhù)一定的Vds電壓Vgs電壓達到最大值,Vds電壓達到最小值,由于Id電流為ID恒定,因此Vds的電壓即為ID和MOSFET的導通電阻的乘積

基于MOSFET的漏極導通特性曲線(xiàn)可以直觀(guān)的理解MOSFET開(kāi)通時(shí),跨越關(guān)斷區、恒流區和可變電阻區的過(guò)程米勒平臺即為恒流區,MOSFET工作于放大狀態(tài),Id電流為Vgs電壓和跨導乘積

電路原理詳細說(shuō)明:

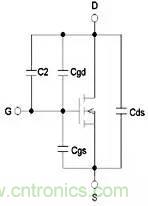

MOS管是電壓控制器件,其極間電容等效電路如圖4所示。

圖4. 帶外接電容C2的N型MOS管極間電容等效電路

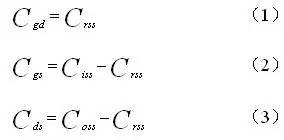

MOS管的極間電容柵漏電容Cgd、柵源電容Cgs、漏源電容Cds可以由以下公式確定:

公式中MOS管的反饋電容Crss,輸入電容Ciss和輸出電容Coss的數值在MOS管的手冊上可以查到。

電容充放電快慢決定MOS管開(kāi)通和關(guān)斷的快慢,Vgs首先給Cgs 充電,隨著(zhù)Vgs的上升,使得MOS管從截止區進(jìn)入可變電阻區。進(jìn)入可變電阻區后,Ids電流增大,但是Vds電壓不變。隨著(zhù)Vgs的持續增大,MOS管進(jìn)入米勒平臺區,在米勒平臺區,Vgs維持不變,電荷都給Cgd 充電,Ids不變,Vds持續降低。在米勒平臺后期,MOS管Vds非常小,MOS進(jìn)入了飽和導通期。為確保MOS管狀態(tài)間轉換是線(xiàn)性的和可預知的,外接電容C2并聯(lián)在Cgd上,如果外接電容C2比MOS管內部柵漏電容Cgd大很多,就會(huì )減小MOS管內部非線(xiàn)性柵漏電容Cgd在狀態(tài)間轉換時(shí)的作用,另外可以達到增大米勒平臺時(shí)間,減緩電壓下降的速度的目的。外接電容C2被用來(lái)作為積分器對MOS管的開(kāi)關(guān)特性進(jìn)行精確控制??刂屏寺O電壓線(xiàn)性度就能精確控制沖擊電流。

電路描述:

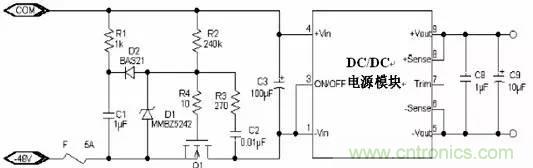

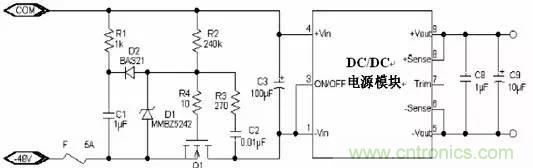

圖5所示為基于MOS管的自啟動(dòng)有源沖擊電流限制法電路。MOS管 Q1放在DC/DC電源模塊的負電壓輸入端,在上電瞬間,DC/DC電源模塊的第1腳電平和第4腳一樣,然后控制電路按一定的速率將它降到負電壓,電壓下降的速度由時(shí)間常數C2*R2決定,這個(gè)斜率決定了最大沖擊電流。

C2可以按以下公式選定:

R2由允許沖擊電流決定:

其中Vmax為最大輸入電壓,Cload為C3和DC/DC電源模塊內部電容的總和,Iinrush為允許沖擊電流的幅度。

圖5 有源沖擊電流限制法電路

D1是一個(gè)穩壓二極管,用來(lái)限制MOS管 Q1的柵源電壓。元器件R1,C1和D2用來(lái)保證MOS管Q1在剛上電時(shí)保持關(guān)斷狀態(tài)。具體情況是:

上電后,MOS管的柵極電壓要慢慢上升,當柵源電壓Vgs高到一定程度后,二極管D2導通,這樣所有的電荷都給電容C1以時(shí)間常數R1×C1充電,柵源電壓Vgs以相同的速度上升,直到MOS管Q1導通產(chǎn)生沖擊電流。

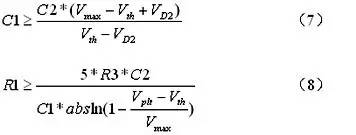

以下是計算C1和R1的公式:

其中Vth為MOS管Q1的最小門(mén)檻電壓,VD2為二極管D2的正向導通壓降,Vplt為產(chǎn)生Iinrush沖擊電流時(shí)的柵源電壓。Vplt可以在MOS管供應商所提供的產(chǎn)品資料里找到。

MOS管選擇

以下參數對于有源沖擊電流限制電路的MOS管選擇非常重要:

l 漏極擊穿電壓 Vds

必須選擇Vds比最大輸入電壓Vmax和最大輸入瞬態(tài)電壓還要高的MOS管,對于通訊系統中用的MOS管,一般選擇Vds≥100V。

l 柵源電壓Vgs

穩壓管D1是用來(lái)保護MOS管Q1的柵極以防止其過(guò)壓擊穿,顯然MOS管Q1的柵源電壓Vgs必須高于穩壓管D1的最大反向擊穿電壓。一般MOS管的柵源電壓Vgs為20V,推薦12V的穩壓二極管。

l 導通電阻Rds_on.

MOS管必須能夠耗散導通電阻Rds_on所引起的熱量,熱耗計算公式為:

其中Idc為DC/DC電源的最大輸入電流,Idc由以下公式確定:

其中Pout為DC/DC電源的最大輸出功率,Vmin為最小輸入電壓,η為DC/DC電源在輸入電壓為Vmin輸出功率為Pout時(shí)的效率。η可以在DC/DC電源供應商所提供的數據手冊里查到。MOS管的Rds_on必須很小,它所引起的壓降和輸入電壓相比才可以忽略。

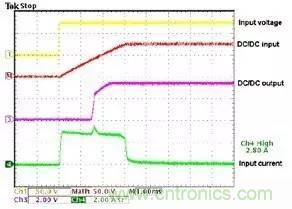

圖6. 有源沖擊電流限制電路在75V輸入,DC/DC輸出空載時(shí)的波形

設計舉例

已知:Vmax=72V

Iinrush=3A

選擇MOS管Q1為IRF540S

選擇二極管D2為BAS21

按公式(4)計算:C2>>1700pF。選擇 C2=0.01μF;

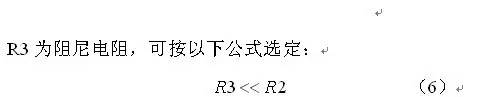

按公式(5)計算:R2=252.5kW。選擇 R2=240kW,選擇R3=270W<

按公式(7)計算:C1=0.75μF。選擇 C1=1μF;

按公式(8)計算:R1=499.5W。選擇 R1=1kW

圖6所示為圖5 電路的實(shí)測波形,其中DC/DC電源輸出為空載。

推薦閱讀: