【導讀】寬禁帶材料實(shí)現了較當前硅基技術(shù)的飛躍。 它們的大帶隙導致較高的介電擊穿,從而降低了導通電阻(RSP)。 更高的電子飽和速度支持高頻設計和工作,降低的漏電流和更好的導熱性有助于高溫下的工作。

安森美半導體提供圍繞寬禁帶方案的獨一無(wú)二的生態(tài)系統,包含從旨在提高強固性和速度的碳化硅(SiC)二極管、SiC MOSFET到 SiC MOSFET的高端IC門(mén)極驅動(dòng)器。 除了硬件以外,我們還提供spice物理模型,幫助設計人員在仿真中實(shí)現其應用性能,縮短昂貴的測試周期。

我們的預測性離散建??梢赃M(jìn)行系統級仿真,其中可以針對系統級性能指標(例如效率)進(jìn)行優(yōu)化,而不局限于優(yōu)化元器件級性能指標,例如RDS(on)。 此外,設計人員可以放心地模擬數據表中未涵蓋的工作條件,例如開(kāi)關(guān)應用的變化溫度、總線(xiàn)電壓、負載電流和輸入門(mén)極電阻。

為滿(mǎn)足這些需求,模型必須是基于物理規律的、直觀(guān)的、可預測的,最重要的是精確的。

在IC行業(yè)中,追溯到幾十年前,采用SPICE模型的支持CAD設計的環(huán)境對于IC設計人員準確預測電路性能至關(guān)重要。 通過(guò)首次正確設計縮短生產(chǎn)周期。 迄今為止,由于缺乏可靠的SPICE模型,電力電子CAD環(huán)境遠遠落后于IC行業(yè)。 電力電子器件模型基于簡(jiǎn)單的子電路和復雜的非物理行為模型。仿真最終不可靠。

圖1

簡(jiǎn)單的子電路過(guò)于基礎簡(jiǎn)單,不足以充分利用所有器件性能。 在圖1中,我們顯示了一個(gè)CRSS圖,將典型的簡(jiǎn)單模型(藍色)與更先進(jìn)的物理模型(綠色)和測量數據(紅色)進(jìn)行了比較。 顯然,您可以看到簡(jiǎn)單模型無(wú)法捕獲非線(xiàn)性電容效應,最終導致不準確的動(dòng)態(tài)開(kāi)關(guān)仿真。

眾所周知,更準確、更復雜的行為模型會(huì )導致收斂問(wèn)題。 此外,此類(lèi)模型通常以專(zhuān)有的仿真器行為語(yǔ)言(例如MAST™)編寫(xiě),因此無(wú)法跨多個(gè)仿真器平臺。

通常,電力電子模型既不是基于工藝技術(shù)和布局的,也不具有芯片平面布局的可擴展性。

我們以物理可擴展模型開(kāi)發(fā)了一個(gè)適用于整個(gè)技術(shù)平臺的模型。 這就是說(shuō),它不是包含經(jīng)驗擬合參數的單個(gè)模型的庫,最終曲線(xiàn)適合所有產(chǎn)品。只需輸入給定產(chǎn)品的芯片平面布局參數,通過(guò)芯片擴展,我們就可以使技術(shù)迅速發(fā)展。

在下一級水平,模型中基于物理學(xué)的工藝依賴(lài)性使我們能夠預測新的虛擬技術(shù)變化帶來(lái)的影響。 顯然,早期設計有助于從應用角度帶動(dòng)技術(shù)要求,并加快產(chǎn)品上市時(shí)間。 一方面,工藝和器件設計工程師使用限定的元器件仿真,也稱(chēng)為T(mén)CAD。 另一方面,應用和系統級設計人員使用基于SPICE的仿真環(huán)境。 基于工藝參數的spice模型有助于這兩方面的融合。

現在,我們介紹一下碳化硅功率MOSFET模型的部分特性。

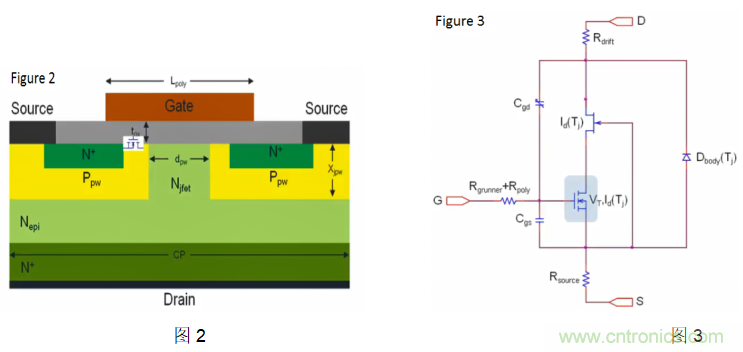

圖2顯示了典型的碳化硅MOSFET橫截面,圖3顯示了子電路模型的簡(jiǎn)化版本。

現在介紹該模型的一些元素。 首先,我們談?wù)勱P(guān)鍵通道區域。 在這里,我們使用著(zhù)名的伯克利BSIM 3v3模型。 我們都盡可能地不做重復工作。 在這種情況下,我們嘗試建模MOSFET通道,該通道非常適合用BSIM模型進(jìn)行。 該模型是基于物理的,通過(guò)亞閾值、弱反演和強反演來(lái)準確捕獲轉換。 此外,它具有出色的速度和收斂性,可以廣泛用于多個(gè)仿真平臺。

接下來(lái),我們需要覆蓋由EPI區域的多晶硅重疊形成的門(mén)極至漏極臨界電容CGD。 該電容本質(zhì)上是高度非線(xiàn)性的金屬氧化物半導體(MOS)電容器。 該電容器的耗盡區由摻雜剖面、P阱dpw之間的距離以及外延層的厚度等工藝參數復雜的依賴(lài)性控制。SPICE行為方法實(shí)施一種基于物理的模型,并將所有這些影響考慮進(jìn)去。

圖4

如圖4所示,從橫截面開(kāi)始,我們想介紹芯片平面圖可擴展性背后的一些概念和結構?;疑珔^域是有源區。 藍色無(wú)源區與裸芯邊緣(die edges)、門(mén)極焊盤(pán)和門(mén)極通道(gate runners)相關(guān)。 基于物理幾何的衍生確定了無(wú)源區和有源區之間的分布,這是實(shí)現可擴展性所需的。 我們非常關(guān)注在有源和無(wú)源區之間的邊界區域中形成的寄生電容。 一旦開(kāi)始忽略布局中的寄生電容,你什么時(shí)候才會(huì )停止這種錯誤呢? 所有被忽略的電容最終累積起來(lái)成為一個(gè)麻煩。 在這種情況下,就無(wú)法實(shí)現擴展。 而我們的理念是不忽略任何電容器。

碳化硅MOSFET支持非??斓膁V / dt,大約每納秒50至100伏,而dI / dts大約每納秒3至6安培。器件固有的門(mén)極電阻很重要,可以用來(lái)抗電磁干擾(EMI)。 圖4右邊的設計具有較少的門(mén)極通道,因此RG較高, 很好地限制了振鈴。 圖4左邊的設計有許多門(mén)極通道,因此RG較低。 左邊的設計適用于快速開(kāi)關(guān),但每個(gè)區域的RDSon也較高,因為門(mén)極通道會(huì )在有源區侵蝕掉。

圖5

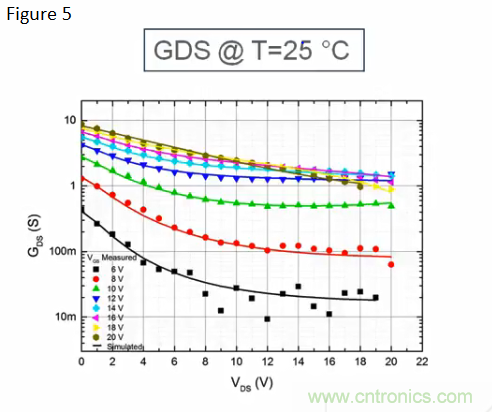

現在,我們要談?wù)勀P万炞C。 我們首先在左側的圖5中顯示輸出電流-電壓特性。該模型準確預測整個(gè)偏置范圍,包括高門(mén)極處的漂移區和漏極偏差。右圖中的精確導通仿真突出了模型的連續性,這對于強固的收斂性能很重要。 除了線(xiàn)性以外,我們經(jīng)常查看對數刻度,以發(fā)現隱藏的不準確和不連續。

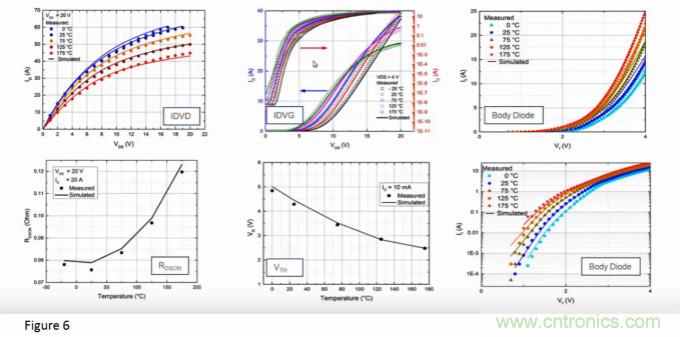

圖6

在圖6中,我們顯示了在寬溫度范圍內的當前電壓、RDSon和閾值電壓的結果。 SiC MOSFET器件具有穩定的溫度性能,因此非常有吸引力。寬溫度范圍內的高精度建模使設計人員可以充分利用這種特性。

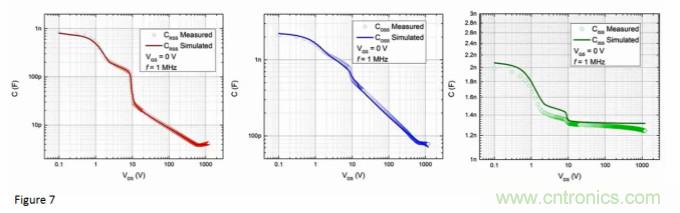

圖7

前面我們介紹了對復雜器件電容的物理建模。 圖7顯示了結果。在左側,CRSS(或CGD)仿真跟蹤數據在2個(gè)數量級以上的多次變化,僅在對數刻度上可見(jiàn)。

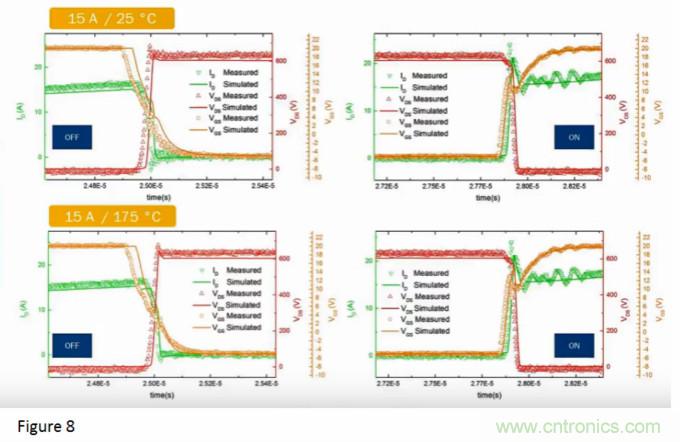

圖8

開(kāi)關(guān)結果具有精確建模的固有電容和器件布局寄生效應,如圖8所示,無(wú)需額外調整模型。 這種水平的保真度使應用設計人員有信心精確地仿真器件電路的相互影響,例如dV / dt、dI / dt、開(kāi)關(guān)損耗和EMI。 門(mén)極驅動(dòng)器和電源環(huán)路的相互作用可以被更進(jìn)一步地研究和優(yōu)化。

對我們來(lái)說(shuō),滿(mǎn)足客戶(hù)各種不同的仿真平臺要求非常重要。 因此,SPICE方法至關(guān)重要。 SPICE不局限于某個(gè)專(zhuān)用平臺或系統,我們僅使用行業(yè)標準仿真軟件中的最小公分母結構,從而避免依賴(lài)于仿真器的專(zhuān)有方案。

安森美半導體提供一系列先進(jìn)的寬禁帶器件和仿真環(huán)境。 完整的產(chǎn)品陣容形成一個(gè)生態(tài)系統,使客戶(hù)能夠充分利用新的、令人興奮的寬禁帶應用和系統。

推薦閱讀: