【導讀】與分立器件相比����,現代集成運算放大器(op amp)和儀表放大器(in-amp)為設計工程師帶來(lái)了許多好處�����。雖然提供了許多巧妙�����、有用并且吸引人的電路����。往往都是這樣�,由于倉促地組裝電路而會(huì )忽視了一些非?���;镜膯?wèn)題�����,從而導致電路不能實(shí)現預期功能 - 或者可能根本不工作����。本文將討論一些最常見(jiàn)的應用問(wèn)題�,并給出實(shí)用的解決方案�。

AC耦合時(shí)缺少DC偏置電流回路

最常遇到的一個(gè)應用問(wèn)題是在交流(AC)耦合運算放大器或儀表放大器電路中沒(méi)有提供偏置電流的直流(DC)回路���。在圖1中�,一只電容器與運算放大器的同相輸入端串聯(lián)以實(shí)現AC耦合�,這是一種隔離輸入電壓(VIN)的DC分量的簡(jiǎn)單方法���。這在高增益應用中尤其有用�����,在那些應用中哪怕運算放大器輸入端很小的直流電壓都會(huì )限制動(dòng)態(tài)范圍���,甚至導致輸出飽和�。然而�����,在高阻抗輸入端加電容耦合����,而不為同相輸入端的電流提供DC通路��,會(huì )出現問(wèn)題�����。

圖1.錯誤的運算放大器AC耦合

實(shí)際上�����,輸入偏置電流會(huì )流入耦合的電容器��,并為它充電�,直到超過(guò)放大器輸入電路的共模電壓的額定值或使輸出達到極限���。根據輸入偏置電流的極性���,電容器會(huì )充電到電源的正電壓或負電壓�����。放大器的閉環(huán)DC增益放大偏置電壓�。

這個(gè)過(guò)程可能會(huì )需要很長(cháng)時(shí)間���。例如����,一只場(chǎng)效應管(FET)輸入放大器�,當1 pA的偏置電流與一個(gè)0.1μF電容器耦合時(shí)�,其充電速率I/C為10–12/10–7=10 μV/s����,或每分鐘600μV�����。如果增益為100��,那么輸出漂移為每分鐘0.06 V����。因此��,一般實(shí)驗室測試(使用AC耦合示波器)無(wú)法檢測到這個(gè)問(wèn)題�,而電路在數小時(shí)之后才會(huì )出現問(wèn)題���。顯然�����,完全避免這個(gè)問(wèn)題非常重要�。

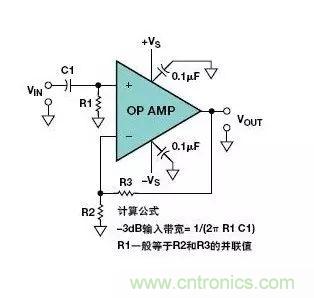

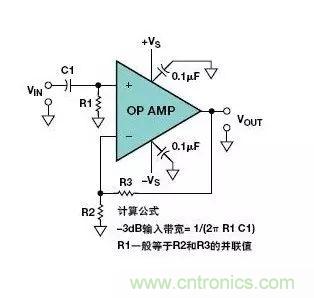

圖2.正確的雙電源供電運算放大器

圖2示出了對這常見(jiàn)問(wèn)題的一種簡(jiǎn)單的解決方案����。這里���,在運算放大器輸入端和地之間接一只電阻器��,為輸入偏置電流提供一個(gè)對地回路����。為了使輸入偏置電流造成的失調電壓最小�,當使用雙極性運算放大器時(shí)���,應該使其兩個(gè)輸入端的偏置電流相等���,所以通常應將R1的電阻值設置成等于R2和R3的并聯(lián)阻值���。

然而�,應該注意的是�,該電阻器R1總會(huì )在電路中引入一些噪聲����,因此要在電路輸入阻抗��、輸入耦合電容器的尺寸和電阻器引起的Johnson噪聲之間進(jìn)行折衷����。典型的電阻器阻值一般在100,000Ω ~1 MΩ之間����。

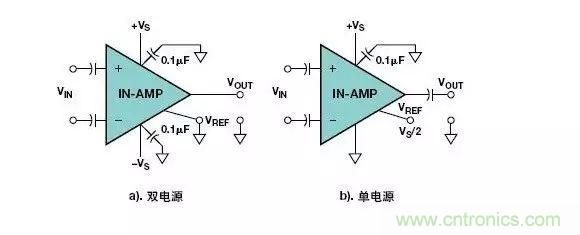

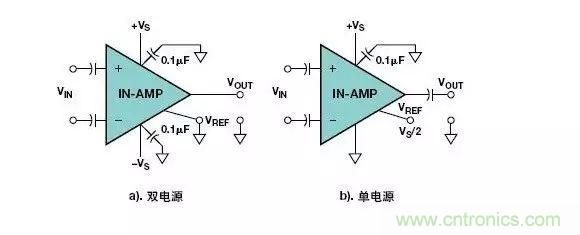

類(lèi)似的問(wèn)題也會(huì )出現在儀表放大器電路中�����。圖3示出了使用兩只電容器進(jìn)行AC耦合的儀表放大器電路���,沒(méi)有提供輸入偏置電流的返回路徑�。這個(gè)問(wèn)題在使用雙電源(圖3a)和單電源(圖3b)供電的儀表放大器電路中很常見(jiàn)����。

圖3.不工作的AC耦合儀表放大器實(shí)例

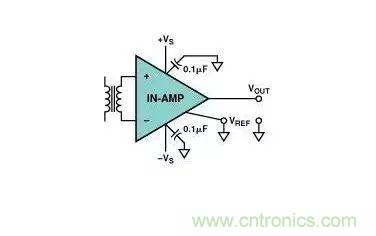

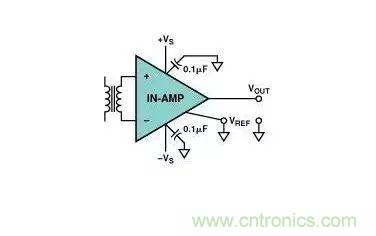

這類(lèi)問(wèn)題也會(huì )出現在變壓器耦合放大器電路中����,如圖4所示��,如果變壓器次級電路中沒(méi)有提供DC對地回路��,該問(wèn)題就會(huì )出現����。

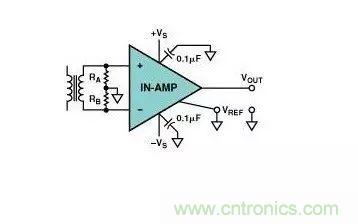

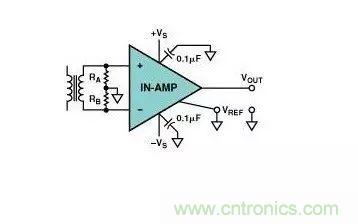

圖4.不工作的變壓器耦合儀表放大器電路

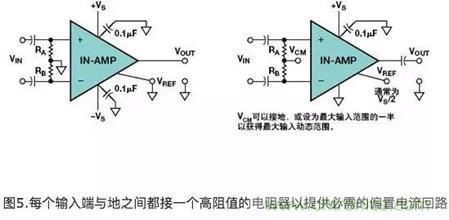

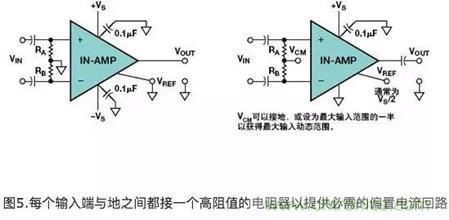

圖5和圖6示出了這些電路的簡(jiǎn)單解決方案���。這里����,在每一個(gè)輸入端和地之間都接一個(gè)高阻值的電阻器(RA�,BR)�����。這是一種適合雙電源儀表放大器電路的簡(jiǎn)單而實(shí)用的解決方案��。

a.雙電源. b.單電源.

這兩只電阻器為輸入偏置電流提供了一個(gè)放電回路�����。在圖5所示的雙電源例子中����,兩個(gè)輸入端的參考端都接地��。在圖5b所示的單電源例子中���,兩個(gè)輸入端的參考端或者接地(VCM接地)或者接一個(gè)偏置電壓����,通常為最大輸入電壓的一半�。

同樣的原則也可以應用到變壓器耦合輸入電路(見(jiàn)圖6)���,除非變壓器的次級有中間抽頭�����,它可以接地或接VCM��。

在該電路中��,由于兩只輸入電阻器之間的失配和(或)兩端輸入偏置電流的失配會(huì )產(chǎn)生一個(gè)小的失調電壓誤差��。為了使失調誤差最小��,在儀表放大器的兩個(gè)輸入端之間可以再接一只電阻器(即橋接在兩只電阻器之間)����,其阻值大約為前兩只電阻器的1/10(但與差分源阻抗相比仍然很大)���。

圖6.正確的儀表放大器變壓器輸入耦合方法

為儀表放大器����、運算放大器和ADC提供參考電壓

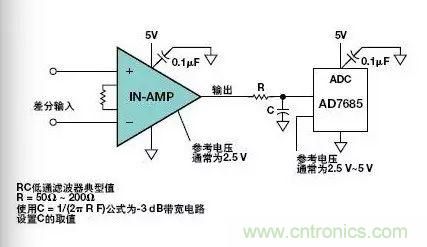

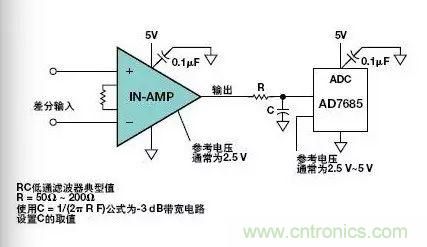

圖7示出一個(gè)儀表放大器驅動(dòng)一個(gè)單端輸入的模數轉換器(ADC)的單電源電路�����。該放大器的參考電壓提供一個(gè)對應零差分輸入時(shí)的偏置電壓���,而ADC的參考電壓則提供比例因子���。在儀表放大器的輸出端和ADC的輸入端之間通常接一個(gè)簡(jiǎn)單的RC低通抗混疊濾波器以減少帶外噪聲���。設計工程師通?���?傁氩捎煤?jiǎn)單的方法���,例如電阻分壓器��,為儀表放大器和ADC提供參考電壓��。因此在使用某些儀表放大器時(shí)�,會(huì )產(chǎn)生誤差��。

圖7.儀表放大器驅動(dòng)ADC的典型單電源電路

正確地提供儀表放大器的參考電壓

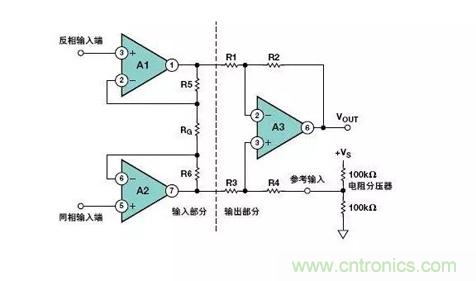

一般假設儀表放大器的參考輸入端為高阻抗��,因為它是一個(gè)輸入端���。所以使設計工程師一般總想在儀表放大器的參考端引腳接入一個(gè)高阻抗源��,例如一只電阻分壓器����。這在某些類(lèi)型儀表放大器的使用中會(huì )產(chǎn)生嚴重誤差(見(jiàn)圖8)��。

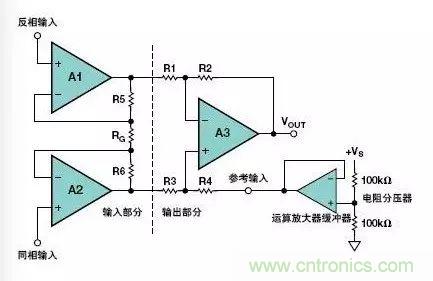

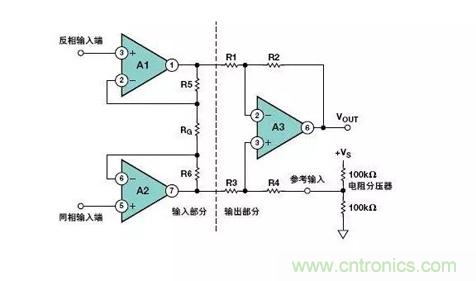

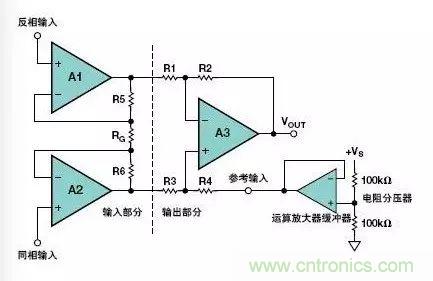

圖8.錯誤地使用一個(gè)簡(jiǎn)單的電阻分壓器直接驅動(dòng)3運放儀表放大器的參考電壓

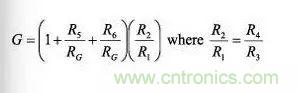

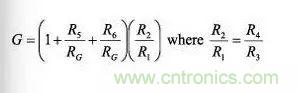

例如����,流行的儀表放大器設計配置使用上圖所示的三運放結構�。其信號總增益為

參考電壓輸入端的增益為1(如果從低阻抗電壓源輸入)�。但是��,在上圖所示的電路中���,儀表放大器的參考輸入端引腳直接與一個(gè)簡(jiǎn)單的分壓器相連����。這會(huì )改變減法器電路的對稱(chēng)性和分壓器的分壓比�。這還會(huì )降低儀表放大器的共模抑制比及其增益精度���。然而�����,如果接入R4,那么該電阻的等效電阻會(huì )變小���,減小的電阻值等于從分壓器的兩個(gè)并聯(lián)支路看過(guò)去的阻值(50 kΩ)���,該電路表現為一個(gè)大小為電源電壓一半的低阻抗電壓源被加在原值R4上�����,減法器電路的精度保持不變�。

如果儀表放大器采用封閉的單封裝形式(一個(gè)IC)�����,則不能使用這種方法��。此外���,還要考慮分壓電阻器的溫度系數應該與R4和減法器中的電阻器保持一致�。最終���,參考電壓將不可調�。另一方面�,如果嘗試減小分壓電阻器的阻值使增加的電阻大小可忽略��,這樣會(huì )增大電源電流的消耗和電路的功耗����。在任何情況下�,這種笨拙的方法都不是好的設計方案����。

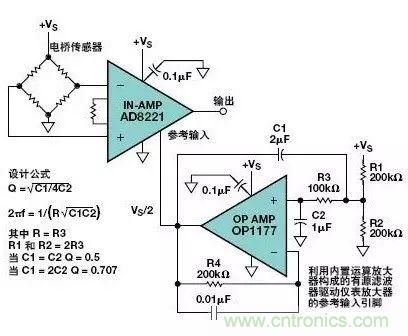

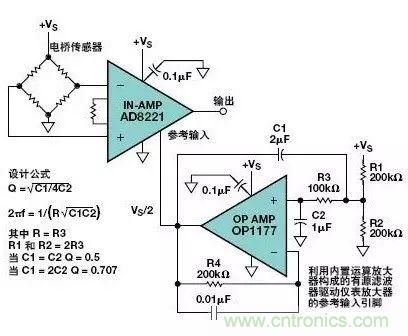

圖9示出了一個(gè)更好的解決方案�,在分壓器和儀表放大器參考電壓輸入端之間加一個(gè)低功耗運算放大器緩沖器��。這會(huì )消除阻抗匹配和溫度系數匹配的問(wèn)題����,而且很容易對參考電壓進(jìn)行調節��。

圖9.利用低輸出阻抗運算放大器驅動(dòng)儀表放大器的參考電壓輸入端

當從電源電壓利用分壓器為放大器提供參考電壓時(shí)應保證PSR性能

一個(gè)經(jīng)常忽視的問(wèn)題是電源電壓VS的任何噪聲�、瞬變或漂移都會(huì )通過(guò)參考輸入按照分壓比經(jīng)過(guò)衰減后直接加在輸出端�����。實(shí)際的解決方案包括旁路濾波以及甚至使用精密參考電壓IC產(chǎn)生的參考電壓���,例如ADR121����,代替VS分壓���。

當設計帶有儀表放大器和運算放大器的電路時(shí)�,這方面的考慮很重要���。電源電壓抑制技術(shù)用來(lái)隔離放大器免受其電源電壓中的交流聲��、噪聲和任何瞬態(tài)電壓變化的影響��。這是非常重要的����,因為許多實(shí)際電路都包含��、連接著(zhù)或存在于只能提供非理想的電源電壓的環(huán)境之中�。另外電力線(xiàn)中的交流信號會(huì )反饋到電路中被放大���,而且在適當的條件下會(huì )引起寄生振蕩��。

現代的運算放大器和儀表放大器都提供頻率相當低的電源電壓抑制(PSR)能力作為其設計的一部分�����。這在大多數工程師看來(lái)是理所當然的��。許多現代的運算放大器和儀表放大器的PSR指標在80~100dB以上��,可以將電源電壓的變化影響衰減到1/10,000~1/100,000���。甚至最適度的40 dB PSR的放大器隔離對電源也可以起到1/100的抑制作用���。不過(guò)�����,總是需要高頻旁路電容(正如圖1~7所示)并且經(jīng)常起到重要作用�。

此外�����,當設計工程師采用簡(jiǎn)單的電源電壓電阻分壓器并且用一只運算放大器緩沖器為儀表放大器提供參考電壓時(shí)�,電源電壓中的任何變化都會(huì )通過(guò)該電路不經(jīng)衰減直接進(jìn)入儀表放大器的輸出級�。因此���,除非提供低通濾波器�����,否則IC通常優(yōu)良的PSR性能會(huì )丟失����。

在圖10中����,在分壓器的輸出端增加一個(gè)大電容器以濾除電源電壓的變化并且保證PSR性能�����。濾波器的-3 dB極點(diǎn)由電阻器R1/R2并聯(lián)和電容器C1決定��。-3 dB極點(diǎn)應當設置在最低有用頻率的1/10處����。

圖10.保證PSR性能的參考端退耦電路

上面示出的CF試用值能夠提供大約0.03 Hz的–3 dB極點(diǎn)頻率���。接在R3兩端的小電容器(0.01 μF)可使電阻器噪聲最小����。

該濾波器充電需要時(shí)間�����。按照試用值���,參考輸入的上升時(shí)間應是時(shí)間常數的幾倍(這里T=R3Cf= 5 s)����,或10~15s����。

圖11中的電路做了進(jìn)一步改進(jìn)�。這里�,運算放大器緩沖器起到一個(gè)有源濾波器的作用����,它允許使用電容值小很多的電容器對同樣大的電源退耦�。此外���,有源濾波器可以用來(lái)提高Q值從而加快導通時(shí)間�。

圖11.將運算放大器緩沖器接成有源濾波器驅動(dòng)儀表放大器的參考輸入引腳

測試結果:利用上圖所示的元件值�����,施加12 V電源電壓�,對儀表放大器的6 V參考電壓提供濾波��。將儀表放大器的增益設置為1�,采用頻率變化的1 VP-P正弦信號調制12 V電源��。在這樣的條件下�����,隨著(zhù)頻率的減小�,一直減到大約8 Hz時(shí)�,我們在示波器上看不到AC信號���。當對儀表放大器施加低幅度輸入信號時(shí)��,該電路的測試電源電壓范圍是4 V到25 V以上�。電路的導通時(shí)間大約為2 s��。

單電源運算放大器電路的退耦

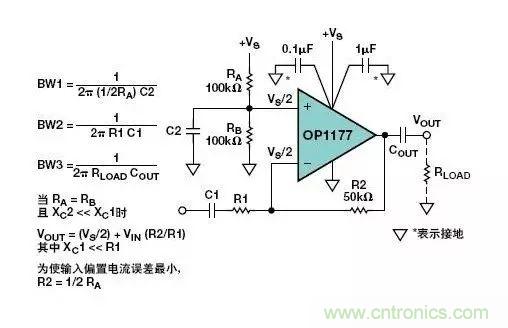

最后�,單電源運算放大器電路需要偏置共模輸入電壓幅度以控制AC信號的正向擺幅和負向擺幅��。當從電源電壓利用分壓器提供偏置電壓時(shí)�,為了保證PSR的性能就需要合適的退耦��。

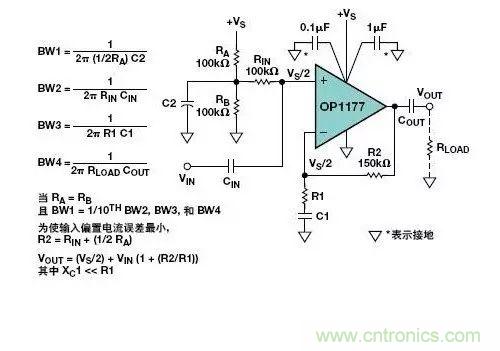

一種常用但不正確的方法是利用100 kΩ/100 kΩ電阻分壓器(加0.1μF旁路電容)提供VS/2給運算放大器的同相輸入端�����。使用這樣小的電容值對電源退耦通常是不夠的�,因為極點(diǎn)僅為32 Hz�。電路出現不穩定(“低頻振蕩”)�����,特別是在驅動(dòng)感性負載時(shí)���。

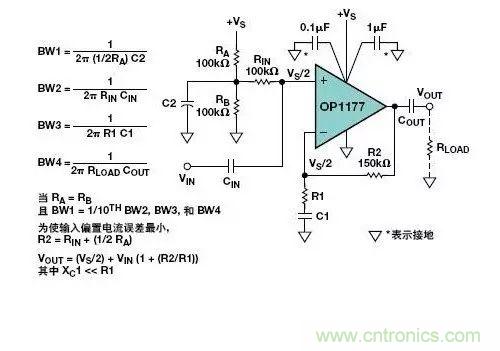

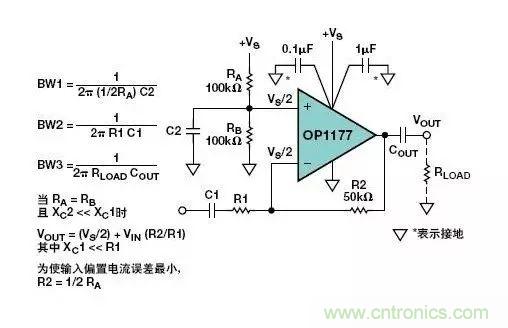

圖12(反相輸入)和圖13(同相輸入)示出了達到最佳退耦結果的VS/2偏置電路��。在兩種情況中��,偏置電壓加在同相輸入端�,反饋到反向輸入端以保證相同的偏置電壓��,并且單位DC增益也要偏置相同的輸出電壓����。耦合電容器C1使低頻增益從BW3降到單位增益��。

圖12.單電源同相輸入放大器電路正確的電源退耦方案��。中頻增益=1+R2/R1

如上圖所示�����,當采用100 kΩ/100 kΩ電阻分壓器時(shí)一個(gè)好的經(jīng)驗是����,為獲得0.3 Hz的–3 dB截止頻率�,應當選用的C2最小為10 ΩF��,��。而100 μF(0.03 Hz)實(shí)際上對所有電路都足夠了���。

圖13.單電源反相輸入放大器正確的退耦電路�,中頻增益= – R2/R1

推薦閱讀: