【導讀】RS-485總線(xiàn)廣泛應用于通信、工業(yè)自動(dòng)化等領(lǐng)域,在實(shí)際應中,通常會(huì )遇到是否需要加上下拉電阻以及加多大的電阻合適的問(wèn)題,下面我們將對這些問(wèn)題進(jìn)行詳細的分析。

RS-485總線(xiàn)廣泛應用于通信、工業(yè)自動(dòng)化等領(lǐng)域,在實(shí)際應中,通常會(huì )遇到是否需要加上下拉電阻以及加多大的電阻合適的問(wèn)題,下面我們將對這些問(wèn)題進(jìn)行詳細的分析。

一、為什么需要加上下拉電阻?

1.當485總線(xiàn)差分電壓大于+200mV時(shí),485收發(fā)器輸出高電平;

2.當485總線(xiàn)差分電壓小于-200mV時(shí),485收發(fā)器輸出低電平;

3.當485總線(xiàn)上的電壓在-200mV~+200mV時(shí),485收發(fā)器可能輸出高電平也可能輸出低電平。但一般總處于一種電平狀態(tài),若485收發(fā)器的輸出低電平,這對于UART通信來(lái)說(shuō)是一個(gè)起始位,此時(shí)通信會(huì )不正常。

當485總線(xiàn)處于開(kāi)路(485收發(fā)器與總線(xiàn)斷開(kāi))或者空閑狀態(tài)(485收發(fā)器全部處于接收狀態(tài),總線(xiàn)沒(méi)有收發(fā)器進(jìn)行驅動(dòng))時(shí),485總線(xiàn)的差分電壓基本為0,此時(shí)總線(xiàn)就處于一個(gè)不確定的狀態(tài)。同時(shí)由于目前485芯片為了提高總線(xiàn)上的節點(diǎn)數,輸入阻抗設計的比較高,例如輸入阻抗為1/4單位阻抗或者1/8單位阻抗(單位阻抗為12kΩ,1/4單位阻抗為48kΩ),在管腳懸空時(shí)容易受到電磁干擾。

因此為了防止485總線(xiàn)出現上述情況,通常在485總線(xiàn)上增加上下拉電阻(通常A接上拉電阻,B總線(xiàn)下拉電阻)。若使用隔離RS-485收發(fā)模塊(例如RSM485PCHT),由于模塊內部具有上下拉電阻(對于RSM485PCHT,內部上下拉電阻為24kΩ),因此在模塊外部一般不需要增加上下拉電阻。

二、什么情況下需要加上下拉電阻?

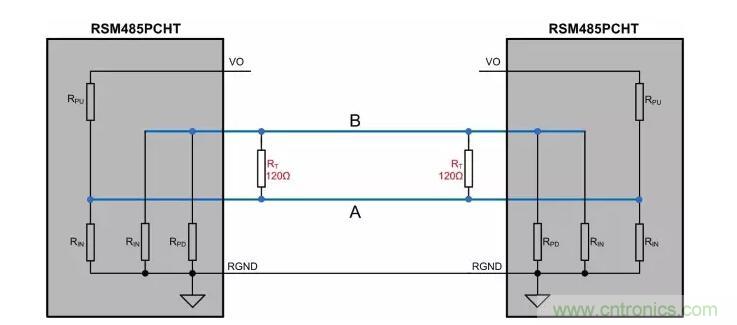

當遇到信號反射問(wèn)題時(shí),通常會(huì )通過(guò)增加匹配電阻來(lái)避免信號反射,以1對1通信為例,如圖1所示。由于485總線(xiàn)通常使用特性阻抗為120Ω的雙絞線(xiàn),因此在485總線(xiàn)的首尾兩端增加120Ω終端電阻來(lái)避免信號反射問(wèn)題。

圖1:兩個(gè)RSM485PCHT模塊通信電路

根據RSM485PCHT的具體參數(如表1)可以得到如圖2所示等效電路,其中RPU、RPD為模塊內部在485總線(xiàn)上加的上下拉電阻,RIN為模塊的輸入阻抗。

表1 RSM485PCHT參數

圖2:RSM485PCHT通信等效示意圖

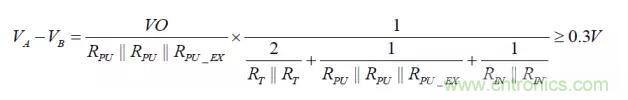

當兩個(gè)模塊都處于接收狀態(tài)時(shí),可以根據基爾霍夫電流定律對節點(diǎn)A和節點(diǎn)B列出下列公式:

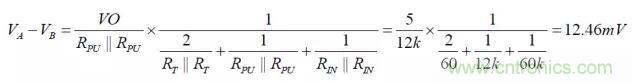

根據上述公式可以計算AB之間的差分電壓為:

此時(shí)模塊已處于不確定狀態(tài),模塊接收器可能輸出為高電平,也可能輸出為低電平,這時(shí)就需要在模塊外部增加上下拉電阻保證模塊在空閑時(shí)不處于不確定狀態(tài)。

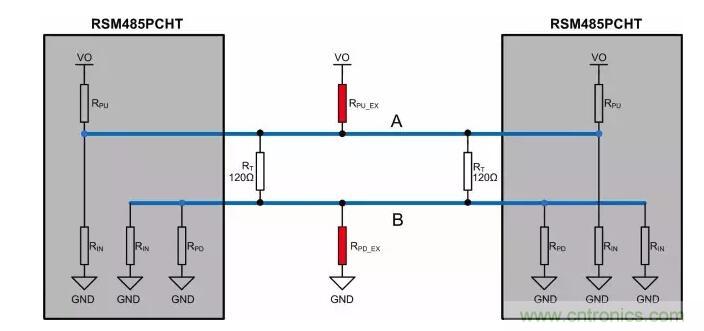

三、上下拉電阻如何???

假設模塊的輸出電源電壓V¬O相同,由于RGND接在一起,因此可以認為模塊內部的上拉電阻是并聯(lián)在一起的,為了方便解釋?zhuān)瑢D2的電路進(jìn)行整理,如圖3所示,在模塊外部增加上下拉電阻可以選擇只增加一組,也可以選擇在每個(gè)模塊都增加上下拉電阻,為了解釋方便,我們在485總線(xiàn)上增加一組上下拉電阻。

圖3 :RSM485PCHT通信等效電路圖

其中:

RPU為模塊內部上拉電阻,RPD為模塊內部的下拉電阻,本例中為24kΩ;

RIN為模塊接收器輸入阻抗,本例取最小值為120kΩ;

RT為終端電阻,本例取120Ω;

RPU_EX為模塊外部所加的上拉電阻,RPD_EX為模塊外部所加的下拉電阻;

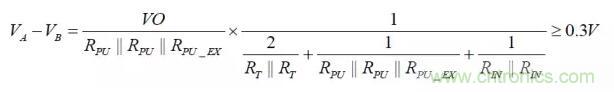

由于RSM485PCHT的門(mén)限電平為-200mV~+200mV,一般留有100mV或200mV的電壓裕量,本例留有100mV的電壓裕量,根據前面所推導的差分電壓公式,可以得到下面計算公式:

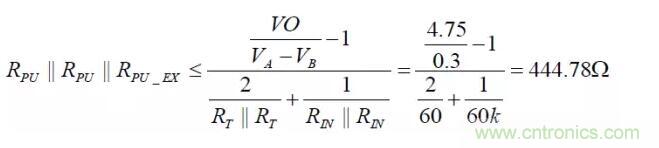

由于RSM485PCHT在供電電壓范圍為4.75V~5.25V,取VO=4.75V(最低輸入電壓VCC=4.75V情況下),可得:

由RPU=24kΩ,可得RPU_EX=RPD_EX=461.9Ω,由于計算出的電阻值為最大值,因此可以選擇在485總線(xiàn)上僅加一組410Ω或390Ω的上下拉電阻,或者加兩組910Ω上下拉電阻。

四、如何驗證上下拉電阻取值?

上述計算僅考慮了485總線(xiàn)空閑狀態(tài)時(shí)不處于不確定狀態(tài),并沒(méi)有考慮485收發(fā)器的驅動(dòng)能力和所用元器件的功耗等問(wèn)題。外部所加上下拉電阻越小,可以將485總線(xiàn)空閑狀態(tài)差分電壓保持的越高,但與此同時(shí),終端電阻和上下拉電阻的功耗也越大,對485收發(fā)器的驅動(dòng)能力要求也越高,當超過(guò)485收發(fā)器的驅動(dòng)能力時(shí),也會(huì )導致通信失敗。

根據RS-485標準,當接收器的輸入阻抗為單位阻抗時(shí)(最小為12k),總線(xiàn)上最多可以接32個(gè)節點(diǎn),485的差分負載最大為54Ω,此時(shí)差分輸出電壓最小為1.5V。

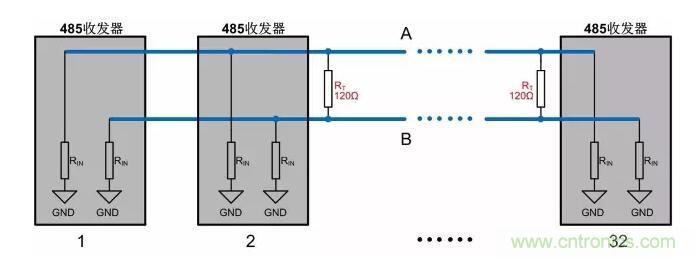

圖4 :485總線(xiàn)連接32個(gè)節點(diǎn)等效示意圖

如圖4所示,我們可以看到當485總線(xiàn)上接有32個(gè)節點(diǎn)時(shí),總線(xiàn)A或B的共模負載為:

由此可見(jiàn),對于RS-485的標準來(lái)說(shuō),A總線(xiàn)或B總線(xiàn)的最大共模負載為375Ω。

圖5 :485總線(xiàn)增加終端電阻等效示意圖

當增加終端電阻后,可以發(fā)現485總線(xiàn)的共模負載沒(méi)有發(fā)生變化,但差模負載急劇減小,差模負載為:

因此當485總線(xiàn)的節點(diǎn)數達到最多以及增加終端電阻后,485總線(xiàn)的差模負載仍大于54Ω,根據RS-485的標準,差分輸出電壓最小為1.5V。

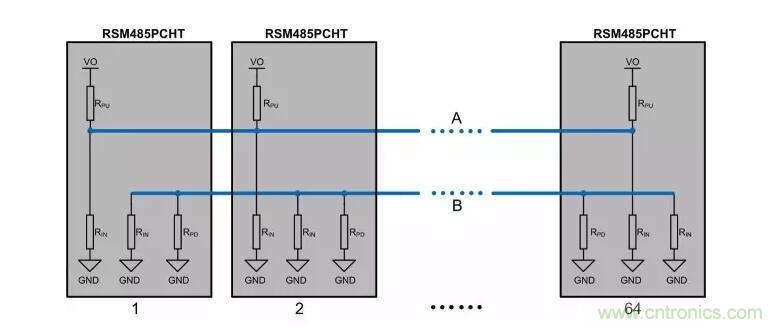

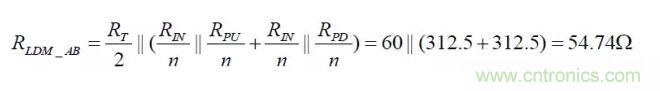

圖6 :RSM485PCHT 64個(gè)節點(diǎn)等效示意圖

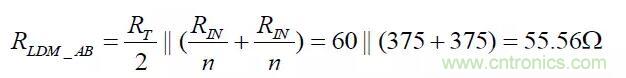

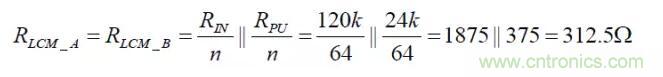

以RSM485PCHT為例說(shuō)明增加上下拉電阻的情況,如圖6所示,總線(xiàn)A或B的共模負載為:

實(shí)際測試上述情況,驅動(dòng)輸出的最小差分電壓3.02V,這個(gè)電壓遠大于RS-485標準規定的最小差分輸出電壓1.5V。

圖7 :RSM485PCHT 64個(gè)節點(diǎn)增加終端電阻示意圖

當在485總線(xiàn)上增加終端電阻時(shí),可以看出總線(xiàn)A或B的共模負載并沒(méi)有發(fā)生變化,而差分阻抗有了較大的變化,此時(shí)差模負載為:

計算出的差模負載要略大于RS-485標準規定的最大負載為54Ω,我們對RSM485PCHT進(jìn)行實(shí)際測試,其輸出差分電壓1.58V,略大于標準規定的最小電壓。

當差模負載為54Ω(485總線(xiàn)接兩個(gè)120Ω終端電阻并且上拉電阻(下拉電阻)與收發(fā)器內阻的并聯(lián)值為270Ω)時(shí),RSM485PCHT的差分輸出電壓為1.52V(實(shí)測值),基本和RS-485標準相同。當差模負載為41.54Ω(485總線(xiàn)接兩個(gè)120Ω終端電阻并且上拉電阻(下拉電阻)與收發(fā)器內阻的并聯(lián)值為135Ω)時(shí),RSM485PCHT的差分輸出電壓在1.17V左右(實(shí)測值),在這種情況下可以通信。但485收發(fā)芯片手冊中規定的最大差模負載通常為54Ω,即在485總線(xiàn)上增加兩個(gè)120Ω后,上拉電阻(下拉電阻)與收發(fā)器輸入阻抗的并聯(lián)值應大于270Ω。同時(shí)為了保證穩定可靠通信,一般485總線(xiàn)的上拉電阻(下拉電阻)與收發(fā)器輸入阻抗的并聯(lián)值應大于375Ω。

五、總結

1.通信線(xiàn)應選用屏蔽雙絞線(xiàn),屏蔽層應單點(diǎn)接大地;

2.當我們沒(méi)有遇到信號反射問(wèn)題時(shí),盡量不要使用終端電阻;

3.如果使用終端電阻,我們可以通過(guò)上下拉電阻調節485總線(xiàn)在空閑狀態(tài)的電壓值,保證不處于門(mén)限電平(-200mV~+200mV或-200mV~-40mV)范圍內;

4.當我們增加上下拉電阻時(shí),上拉電阻(下拉電阻)與收發(fā)器輸入阻抗的并聯(lián)值應大于375Ω。