【導讀】比較SiC開(kāi)關(guān)的數據資料并非易事。由于導通電阻的溫度系數較低,SiC MOSFET似乎占據了優(yōu)勢,但是這一指標也代表著(zhù)與UnitedSiC FET相比,它的潛在損耗較高,整體效率低。

諺語(yǔ)說(shuō):“不怕低,只怕比”。這條諺語(yǔ)首次出現在1440年約翰·利德蓋特的《馬鵝羊之間的辯論》中。疲于比較的不僅僅是文章中的動(dòng)物,現代功率轉換器設計師們也不得不拼命從大量競爭性主張中嘗試找出適合他們的應用的功率開(kāi)關(guān),并進(jìn)行比較,以獲得“最佳性能”。如果繼續以農牧業(yè)來(lái)比喻,這個(gè)問(wèn)題就像是將一個(gè)蘋(píng)果與一堆蘋(píng)果相比較,因為如果不考慮與其他指標的權衡取舍,就不能評價(jià)任何單個(gè)電子參數的好壞。開(kāi)關(guān)導通電阻就是一個(gè)好例子,你必須在相同的額定電壓下,在各個(gè)制造商的建議柵極驅動(dòng)電壓下,在相同的結溫和漏極電流下,在相同的封裝中比較零件,才能了解這個(gè)參數。

Si-MOSFET、SiC-MOSFET和SiC FET競爭上崗

在不低于幾百伏的較高電壓下,Si MOSFET、SiC MOSFET和UnitedSiC FET是同一個(gè)位置的有力競爭產(chǎn)品,它們的數據資料中通常標明特定額定電壓、結溫和柵極驅動(dòng)電壓下的RDS(ON)值。例如,UnitedSiC最近推出的零件UJ4C075018K4S就提供了在VGS = 12V、溫度為25°C至175°C、漏極電流為20A時(shí)的導通電阻值。從中,您可以輕松獲得該零件在給定溫度下的RDS(ON)溫度系數數值,在Tj =125°C時(shí),該數值約為+70-75%。

650V SiC MOSFET的擁護者可能會(huì )指出,他們發(fā)現其他類(lèi)似器件在Tj =125°C下的該數值通常為+20-25%。這能說(shuō)明SiC MOSFET比其他器件好三倍嗎?恐怕不能這么武斷。首先,部分正溫度系數值是必要的,可以迫使晶粒中的單元分擔電流,而不會(huì )出現熱點(diǎn)和熱散逸。同理,設計師依靠正值才能并聯(lián)器件,并自然分流。

SiC MOSFET的電阻由其反型溝道決定

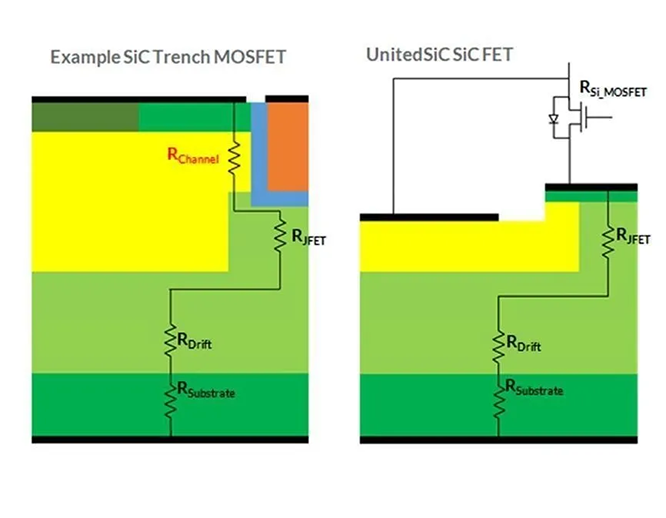

SiC MOSFET較低的RDS(ON)溫度系數值實(shí)際上表明會(huì )出現較深層次的影響。MOSFET和JFET是“單載流子”器件,電子流會(huì )經(jīng)過(guò)不同區(基質(zhì)、漂移層、JFET區和溝道等)。在650V SiC MOSFET中,反型溝道決定了總電阻,而總電阻實(shí)際上會(huì )隨著(zhù)溫度降低。溝道電阻與自由載流子數和反型層電子遷移率的乘積成反比。隨著(zhù)溫度升高,閾值電壓會(huì )降低,而溝道中的自由載流子數會(huì )增加,因而電阻會(huì )降低。其余器件區(即JFET、漂移層和基質(zhì)電阻)的正溫度系數會(huì )抵消這種影響,從而產(chǎn)生不高的凈正Tc值。在SiC JFET中,沒(méi)有反型溝道來(lái)抵消JFET、漂移層和基質(zhì)的正溫度系數。同時(shí),低壓Si MOSFET僅占總導通電阻的一小部分,這解釋了為什么采用它時(shí)的Tc值比采用SiC MOSFET時(shí)要高,不過(guò)有說(shuō)服力的一點(diǎn)是,SiC FET中不存在由不理想的SiC反型層造成的損耗(圖1)。

【圖1:典型的SiC MOSFET溝槽結構和沒(méi)有大損耗SiC MOS反型溝道的UnitedSiC FET,后者有較高的導通電阻溫度系數,但是損耗較低】

SiC FET的整體導電損耗較低

如果審視絕對值,則會(huì )發(fā)現決定性的證據。如圖2所示,在比較650/750V器件的RDS(ON)時(shí),在25°C時(shí),UnitedSiC FET的導通電阻大約是SiC MOSFET的三分之一,優(yōu)勢最明顯,在150°C時(shí),仍比后者好2倍左右,在相同有效晶粒面積下,前者帶來(lái)的導電損耗大約是后者的一半。

【圖2:UnitedSiC FET導通電阻的Tc較高,但是絕對值較低】

采用UnitedSiC FET的最終效果是整體導電損耗較低,且RDS(ON)的正溫度系數十分健康,可確保單元和并聯(lián)器件之間實(shí)現有效分流。很明顯,確保合理進(jìn)行比較并理解這種效果背后的機制是值得的,它揭示了什么才是真正重要的,那就是較低的整體損耗。

文章來(lái)源: UnitedSiC

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請聯(lián)系小編進(jìn)行處理。

推薦閱讀: