【導讀】本文就旁路電容、電源、地線(xiàn)設計、電壓誤差和由PCB布線(xiàn)引起的電磁干擾(EMI)等幾個(gè)方面,討論模擬和數字布線(xiàn)的基本相似之處及差別。

工程領(lǐng)域中的數字設計人員和數字電路板設計專(zhuān)家在不斷增加,這反映了行業(yè)的發(fā)展趨勢。盡管對數字設計的重視帶來(lái)了電子產(chǎn)品的重大發(fā)展,但仍然存在,而且還會(huì ) 一直存在一部分與模擬或現實(shí)環(huán)境接口的電路設計。模擬和數字領(lǐng)域的布線(xiàn)策略有一些類(lèi)似之處,但要獲得更好的結果時(shí),由于其布線(xiàn)策略不同,簡(jiǎn)單電路布線(xiàn)設計 就不再是最優(yōu)方案了。本文就旁路電容、電源、地線(xiàn)設計、電壓誤差和由PCB布線(xiàn)引起的電磁干擾(EMI)等幾個(gè)方面,討論模擬和數字布線(xiàn)的基本相似之處及 差別。

模擬和數字布線(xiàn)策略的相似之處

旁路或去耦電容

在布線(xiàn)時(shí),模擬器件和數字器件都需要這些類(lèi)型的電容,都需要靠近其電源引腳連接一個(gè)電容,此電容值通常為0.1uF。系統供電電源側需要另一類(lèi)電容,通常此電容值大約為10uF。

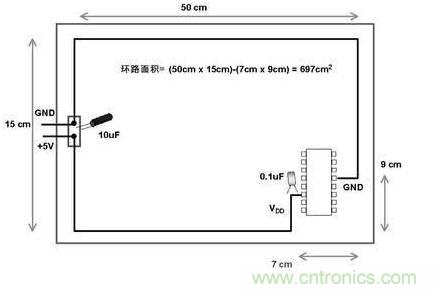

這些電容的位置如圖1所示。電容取值范圍為推薦值的1/10至10倍之間。但引腳須較短,且要盡量靠近器件(對于0.1uF電容)或供電電源(對于10uF電容)。

在電路板上加旁路或去耦電容,以及這些電容在板上的位置,對于數字和模擬設計來(lái)說(shuō)都屬于常識。但有趣的是,其原因卻有所不同。在模擬布線(xiàn)設計中,旁路電容通 常用于旁路電源上的高頻信號,如果不加旁路電容,這些高頻信號可能通過(guò)電源引腳進(jìn)入敏感的模擬芯片。一般來(lái)說(shuō),這些高頻信號的頻率超出模擬器件抑制高頻信 號的能力。如果在模擬電路中不使用旁路電容的話(huà),就可能在信號路徑上引入噪聲,更嚴重的情況甚至會(huì )引起振動(dòng)。

圖1 在模擬和數字PCB設計中,旁路或去耦電容(0.1uF)應盡量靠近器件放置。供電電源去耦電容(10uF)應放置在電路板的電源線(xiàn)入口處。所有情況下,這些電容的引腳都應較短

圖2 在此電路板上,使用不同的路線(xiàn)來(lái)布電源線(xiàn)和地線(xiàn),由于這種不恰當的配合,電路板的電子元器件和線(xiàn)路受電磁干擾的可能性比較大

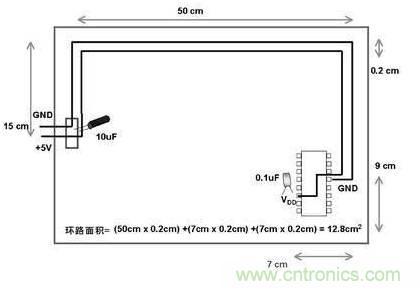

圖3 在此單面板中,到電路板上器件的電源線(xiàn)和地線(xiàn)彼此靠近。此電路板中電源線(xiàn)和地線(xiàn)的配合比圖2中恰當。電路板中電子元器件和線(xiàn)路受電磁干擾(EMI)的可能性降低了679/12.8倍或約54倍

對于控制器和處理器這樣的數字器件,同樣需要去耦電容,但原因不同。這些電容的一個(gè)功能是用作“微型”電荷庫。在數字電路中,執行門(mén)狀態(tài)的切換通常需要很大 的電流。由于開(kāi)關(guān)時(shí)芯片上產(chǎn)生開(kāi)關(guān)瞬態(tài)電流并流經(jīng)電路板,有額外的“備用”電荷是有利的。如果執行開(kāi)關(guān)動(dòng)作時(shí)沒(méi)有足夠的電荷,會(huì )造成電源電壓發(fā)生很大變 化。電壓變化太大,會(huì )導致數字信號電平進(jìn)入不確定狀態(tài),并很可能引起數字器件中的狀態(tài)機錯誤運行。流經(jīng)電路板走線(xiàn)的開(kāi)關(guān)電流將引起電壓發(fā)生變化,電路板走 線(xiàn)存在寄生電感,可采用如下公式計算電壓的變化:V = LdI/dt

其中,V = 電壓的變化;L = 電路板走線(xiàn)感抗;dI = 流經(jīng)走線(xiàn)的電流變化;dt =電流變化的時(shí)間。

因此,基于多種原因,在供電電源處或有源器件的電源引腳處施加旁路(或去耦)電容是較好的做法。

電源線(xiàn)和地線(xiàn)要布在一起

電源線(xiàn)和地線(xiàn)的位置良好配合,可以降低電磁干擾的可能性。如果電源線(xiàn)和地線(xiàn)配合不當,會(huì )設計出系統環(huán)路,并很可能會(huì )產(chǎn)生噪聲。電源線(xiàn)和地線(xiàn)配合不當的PCB設計示例如圖2所示。

此電路板上,設計出的環(huán)路面積為697cm2。采用圖3所示的方法,電路板上或電路板外的輻射噪聲在環(huán)路中感應電壓的可能性可大為降低。

模擬和數字領(lǐng)域布線(xiàn)策略的不同之處

地平面是個(gè)難題

電路板布線(xiàn)的基本知識既適用于模擬電路,也適用于數字電路。一個(gè)基本的經(jīng)驗準則是使用不間斷的地平面,這一常識降低了數字電路中的dI/dt(電流隨時(shí)間的 變化)效應,這一效應會(huì )改變地的電勢并會(huì )使噪聲進(jìn)入模擬電路。數字和模擬電路的布線(xiàn)技巧基本相同,但有一點(diǎn)除外。對于模擬電路,還有另外一點(diǎn)需要注意,就 是要將數字信號線(xiàn)和地平面中的回路盡量遠離模擬電路。這一點(diǎn)可以通過(guò)如下做法來(lái)實(shí)現:將模擬地平面單獨連接到系統地連接端,或者將模擬電路放置在電路板的 最遠端,也就是線(xiàn)路的末端。這樣做是為了保持信號路徑所受到的外部干擾最小。對于數字電路就不需要這樣做,數字電路可容忍地平面上的大量噪聲,而不會(huì )出現 問(wèn)題。

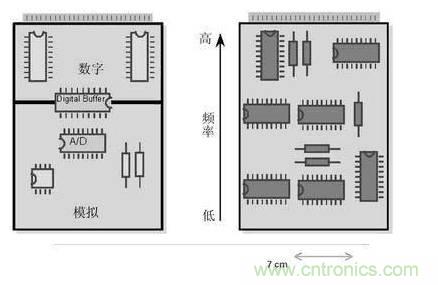

圖4 (左)將數字開(kāi)關(guān)動(dòng)作和模擬電路隔離,將電路的數字和模擬部分分開(kāi)。 (右) 要盡可能將高頻和低頻分開(kāi),高頻元件要靠近電路板的接插件

圖5 在PCB上布兩條靠近的走線(xiàn),很容易形成寄生電容。由于這種電容的存在,在一條走線(xiàn)上的快速電壓變化,可在另一條走線(xiàn)上產(chǎn)生電流信號

圖6 如果不注意走線(xiàn)的放置,PCB中的走線(xiàn)可能產(chǎn)生線(xiàn)路感抗和互感。這種寄生電感對于包含數字開(kāi)關(guān)電路的電路運行是非常有害的

元件的位置

如上所述,在每個(gè)PCB設計中,電路的噪聲部分和“安靜”部分(非噪聲部分)要分隔開(kāi)。一般來(lái)說(shuō),數字電路“富含”噪聲,而且對噪聲不敏感(因為數字電路有 較大的電壓噪聲容限);相反,模擬電路的電壓噪聲容限就小得多。兩者之中,模擬電路對開(kāi)關(guān)噪聲最為敏感。在混合信號系統的布線(xiàn)中,這兩種電路要分隔開(kāi),如 圖4所示。

PCB設計產(chǎn)生的寄生元件

PCB設計中很容易形成可能產(chǎn)生問(wèn)題的兩種基本寄生元件:寄生電容和寄生電感。設計 電路板時(shí),放置兩條彼此靠近的走線(xiàn)就會(huì )產(chǎn)生寄生電容??梢赃@樣做:在不同的兩層,將一條走線(xiàn)放置在另一條走線(xiàn)的上方;或者在同一層,將一條走線(xiàn)放置在另一 條走線(xiàn)的旁邊,如圖5所示。在這兩種走線(xiàn)配置中,一條走線(xiàn)上電壓隨時(shí)間的變化(dV/dt)可能在另一條走線(xiàn)上產(chǎn)生電流。如果另一條走線(xiàn)是高阻抗的,電場(chǎng) 產(chǎn)生的電流將轉化為電壓。

快速電壓瞬變最常發(fā)生在模擬信號設計的數字側。如果發(fā)生快速電壓瞬變的走線(xiàn)靠近高阻抗模擬走線(xiàn),這種誤差將嚴重影響模擬電路的精度。在這種環(huán)境中,模擬電路有兩個(gè)不利的方面:其噪聲容限比數字電路低得多;高阻抗走線(xiàn)比較常見(jiàn)。

采用下述兩種技術(shù)之一可以減少這種現象。最常用的技術(shù)是根據電容的方程,改變走線(xiàn)之間的尺寸。要改變的最有效尺寸是兩條走線(xiàn)之間的距離。應該注意,變量d在 電容方程的分母中,d增加,容抗會(huì )降低??筛淖兊牧硪粋€(gè)變量是兩條走線(xiàn)的長(cháng)度。在這種情況下,長(cháng)度L降低,兩條走線(xiàn)之間的容抗也會(huì )降低。

另一種技術(shù)是在這兩條走線(xiàn)之間布地線(xiàn)。地線(xiàn)是低阻抗的,而且添加這樣的另外一條走線(xiàn)將削弱產(chǎn)生干擾的電場(chǎng),如圖5所示。

電路板中寄生電感產(chǎn)生的原理與寄生電容形成的原理類(lèi)似。也是布兩條走線(xiàn),在不同的兩層,將一條走線(xiàn)放置在另一條走線(xiàn)的上方;或者在同一層,將一條走線(xiàn)放置在 另一條的旁邊,如圖6所示。在這兩種走線(xiàn)配置中,一條走線(xiàn)上電流隨時(shí)間的變化(dI/dt),由于這條走線(xiàn)的感抗,會(huì )在同一條走線(xiàn)上產(chǎn)生電壓;并由于互感 的存在,會(huì )在另一條走線(xiàn)上產(chǎn)生成比例的電流。如果在第一條走線(xiàn)上的電壓變化足夠大,干擾可能會(huì )降低數字電路的電壓容限而產(chǎn)生誤差。并不只是在數字電路中才 會(huì )發(fā)生這種現象,但這種現象在數字電路中比較常見(jiàn),因為數字電路中存在較大的瞬時(shí)開(kāi)關(guān)電流。

為消除電磁干擾源的潛在噪聲,最好將“安靜”的模擬線(xiàn)路和噪聲I/O端口分開(kāi)。要設法實(shí)現低阻抗的電源和地網(wǎng)絡(luò ),應盡量減小數字電路導線(xiàn)的感抗,盡量降低模擬電路的電容耦合。

結語(yǔ)

數字和模擬范圍確定后,謹慎地布線(xiàn)對獲得成功的PCB至關(guān)重要。布線(xiàn)策略通常作為經(jīng)驗準則向大家介紹,因為很難在實(shí)驗室環(huán)境中測試出產(chǎn)品的最終成功與否。因此,盡管數字和模擬電路的布線(xiàn)策略存在相似之處,還是要認識到并認真對待其布線(xiàn)策略的差別。

推薦閱讀: