【導讀】Apple Watch搭載的是S1芯片,在這款尺寸為 26 毫米×28 毫米的芯片內有 30 個(gè)獨立的組件,這絕對稱(chēng)得上“讓人驚嘆”。今天我們一起從更專(zhuān)業(yè)的角度來(lái)了解這款芯片。

Apple Watch搭載的是S1芯片,在這款尺寸為 26 毫米×28 毫米的芯片內有 30 個(gè)獨立的組件,這絕對稱(chēng)得上“讓人驚嘆”。其中還包括了 NXP 的 NFC 芯片、AMS 的 NFC 信號放大器及Maxin的音頻放大器。今天外媒與我們一起從更專(zhuān)業(yè)的角度來(lái)了解這款芯片。目前開(kāi)發(fā)和銷(xiāo)售智能手表的 OEM 很多都是智能手機廠(chǎng)商,所以我們會(huì )看到這些廠(chǎng)商通常都是直接將智能手機的部件“塞到”智能手表里面。

很多Android Wear 手表使用的都是調制解調器的高通 Snapdragon 400 芯片。而 A7 芯片從散熱設計功耗的角度來(lái)說(shuō)是適合智能手表的。Android Wear 手表的電池容量大約為 400 mAh,可續航 1-2 天,但是對于市場(chǎng)來(lái)說(shuō)這些手表太大,這種時(shí)候就需要特別針對智能手表的外形和大小設計的 SoC 片上系統。

對于 Apple Watch S1 芯片,目前還沒(méi)有合適的跑分測試工具,但是從這款設備的拆解我們可以看到,該 SoC 使用的是三星 28nm LP 制程,使用的只可能是 HKMG 或 poly SiON 柵極結構。選擇不同的結構功率效率也會(huì )不同,因為 HKMG 制程的漏泄功率更小。和使用 20/14nm 制程的成本相比,這兩種制程的成本差異并不大,另外參考 TSMC 在 Snapdragon 600 和 800 芯片上從 28LP 制程換成 28HPm 后對電池續航的影響,基本可以確定蘋(píng)果的這款芯片使用的是 HKMG 制程。

我們也已經(jīng)知道二進(jìn)制文件是為手表的 ARMv7k 處理器進(jìn)行編譯,可惜目前關(guān)于該指令集架構并沒(méi)有相關(guān)記錄。watchOS 是在 iOS/Darwin 的基礎上開(kāi)發(fā)出來(lái)的,也就是說(shuō)為了獲得存儲保護和關(guān)鍵抽象,比如虛擬內存,它需要內存管理單元MMU,這就排除了使用像 ARMv7m 這樣的 MCU ISA 的可能性,我們猜測蘋(píng)果使用的可能是衍生的 ARMv7-A,精簡(jiǎn)掉不必要的指令,以減小功率消耗。

至于設備的 GPU 就不那么神秘了,從出現在 Apple Watch 中的 PowerVR 驅動(dòng)器來(lái)看,S1使用的可能是 PowerVR Series 5 GPU,具體哪款尚未清楚,有可能是 PowerVR SGX543MP1。不過(guò)我更傾向于 PowerVR GX5300,因為它是特別針對穿戴設備優(yōu)化的 GPU,使用的驅動(dòng)器也一樣。但是不管怎樣,在 watchOS 2 到來(lái)之前 Apple Watch 都無(wú)法原生運行應用這一點(diǎn)來(lái)看,我們目前能夠深入挖掘的東西很少,而且即使 watchOS 2 發(fā)布,圖形跑分可能還是不好測試。

[page]

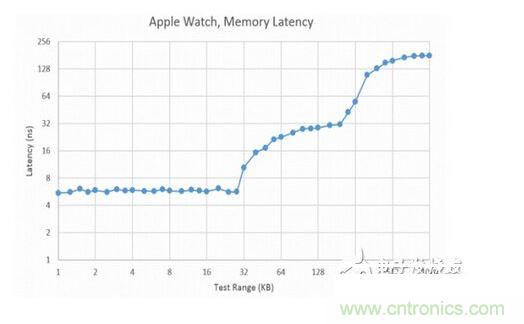

接下來(lái)我們可以來(lái)了解一下 CPU 的分級存儲器體系,對于需要優(yōu)化以確保代碼能有足夠時(shí)間和/或空間局部性來(lái)保證代碼性能的應用來(lái)說(shuō),這是一項非常重要的信息。

如圖所示, 在 DRAM 28KB 和 64KB 之間有一個(gè)非常大的波動(dòng)變化,因為我們已經(jīng)清除了 L1 數據緩存的本地最大值,我們基本可以確定 L1 數據緩存大小為32KB,目前市場(chǎng)上很多產(chǎn)品的 L1 數據緩存也在 32 和 64KB 之間。而在 224KB 左右的地方再次出現大變化,我們也可以確定 L2 的數據緩存為 256KB,和目前大型智能手機 CPU 的 1-2MB 共享緩存相比小了很多,但是和 A5 或者 A7 相比則恰好合適。

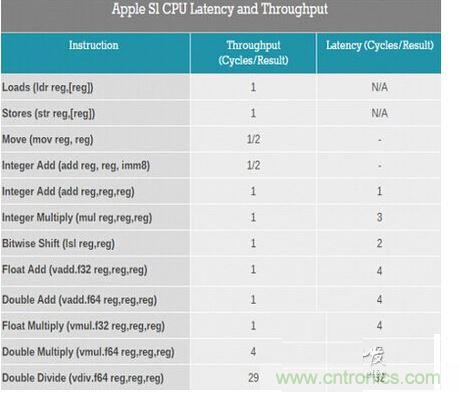

Apple Watch 的 CPU 最大頻率是520 MHz。我們接下來(lái)看看它的架構。在關(guān)于整數運算這方面,整數添加延遲是一個(gè)循環(huán),而整數乘法延遲則是三個(gè)循環(huán)。但是因為流水線(xiàn)整數乘法的吞吐量能輸出一個(gè)時(shí)鐘周期結果。同樣的比特移位需要兩個(gè)周期來(lái)完成,而吞吐只需要一個(gè)時(shí)鐘周期。乘法和加法交錯吞吐量將只有一半。我們可以猜測這是因為整數加法 block 和整數乘法 block 相同,然而這并沒(méi)有什么意義,因為從邏輯層面來(lái)說(shuō),加法和乘法區別太大了。

從數據類(lèi)型的角度來(lái)說(shuō),整數只是一個(gè)因素,還有布爾值、字符、字符串和不同大小的整數,但是說(shuō)到十進(jìn)制,應用程序仍然使用浮點(diǎn)來(lái)編譯。像這款低功率 CPU,浮點(diǎn)通常比整數慢,因為浮點(diǎn)運算的相關(guān)法則比較復雜。

如果你打開(kāi)的網(wǎng)頁(yè)的延遲和吞吐時(shí)間是針對 Cortex A7 的,你可能猜測它是 Cortex A7,那你可能就猜對了。同時(shí)加載存儲意味著(zhù)這些是 XOR 運算,不能以平行方式執行。乘法運算和加法運算也是一樣。雖然 Cortex A7 和 Cortex A5 有相同點(diǎn),但也不能說(shuō)明為什么可以每時(shí)鐘周期可增加兩次立即值/恒定值和累加寄存器。

從這些數據我們可以確定它就是單核 Cortex A7。雖然只是 Cortex A7 但是最大時(shí)鐘速度較低,也就是說(shuō)邏輯設計上相比性能他更重視功率效率。標準電池可以利用某些技術(shù)和風(fēng)格,這些技術(shù)實(shí)際會(huì )影響 2+ GHz 芯片的性能,但是卻非常適合使用在 520 MHz 芯片中、從衡量能源效率與性能的角度來(lái)說(shuō),Cortex A7 是一個(gè)有利于 perf/W(Performance per Watt,每瓦性能)的設計,因此我認為未來(lái)關(guān)鍵的不同點(diǎn)將在于執行方法,而不是架構。雖然我也希望 Apple Watch 能夠使用更為先進(jìn)的制程,比如 14LPP/16FF+,但是在 Apple Watch 第二代或者第三代出來(lái)之前基本都沒(méi)有這種可能。