【導讀】設計并調試鎖相環(huán)(PLL)電路可能會(huì )很復雜,除非工程師深入了解 PLL 理論以及邏輯開(kāi)發(fā)過(guò)程。本文介紹 PLL 設計的簡(jiǎn)易方法,并提供有效、符合邏輯的方法調試 PLL 問(wèn)題。

仿真

如果不在特定條件下進(jìn)行仿真,則估計一個(gè) PLL 電路的規格將會(huì )是十分困難的。因此,進(jìn)行 PLL 設計的第一步應當是仿真。我們建議工程師使用ADIsimPLL 軟件運行基于系統要求的仿真,包括參考頻率、步進(jìn)頻率、相位噪聲(抖動(dòng))和頻率雜散限制。

許多工程師面對如何選擇參考頻率會(huì )感到無(wú)所適從,但其實(shí)參考頻率和輸出頻率步進(jìn)之間的關(guān)系是很簡(jiǎn)單的。采用整數 N 分頻 PLL,則輸出頻率步進(jìn)等于鑒頻鑒相器(PFD)輸入端的頻率,該頻率等于參考分頻器 R 分頻后的參考頻率。采用小數 N 分頻 PLL,則輸出頻率步進(jìn)等于 PFD 輸入頻率除以 MOD 值,因此,您可以使用較高的參考頻率,獲得較小的頻率步進(jìn)。決定使用整數 N 分頻或是小數 N 分頻時(shí),可犧牲相位噪聲性能換取頻率步進(jìn),即:較低的 PFD 頻率具有更好的輸出頻率分辨率,但相位噪聲性能下降。

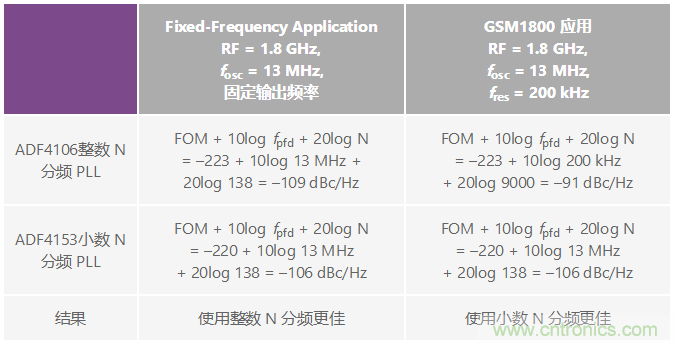

例如,表1顯示若要求具有固定頻率輸出以及極大的頻率步進(jìn),則應首選整數 N 分頻 PLL(如ADF4106),因為它具有更佳的總帶內相位噪聲。相反,若要求具有較小的頻率步進(jìn),則應首選小數 N 分頻 PLL(如ADF4153),因為它的總噪聲性能優(yōu)于整數 N 分頻 PLL。相位噪聲是一個(gè)基本的 PLL 規格,但數據手冊無(wú)法針對所有可能的應用指定性能參數。因此,先仿真,然后進(jìn)行實(shí)際硬件的測試就變得極為關(guān)鍵。

表1. 相位噪聲確定 PLL 的選擇

甚至在真實(shí)條件下通過(guò) ADIsimPLL 仿真 PLL 電路時(shí),結果也可能是不夠的,除非真實(shí)參考以及壓控振蕩器(VCO)的模型文件已包含在內。如果未包含在內,則仿真器將使用理想參考和VCO 進(jìn)行仿真。若要求高仿真精度,則花在編輯 VCO 和基準電壓源庫文件上的時(shí)間將會(huì )是值得的。

PLL 使用與放大器類(lèi)似的負反饋控制系統,因此環(huán)路帶寬和相位裕量的概念此處依然適用。通常,環(huán)路帶寬應設為 PFD 頻率的十分之一以下,且相位裕量的安全范圍為 45°至 60°。此外,應當進(jìn)行針對真實(shí)電路板的仿真和原型制作,以便確認電路符合 PCB 布局對寄生元件、電阻容差和環(huán)路濾波器電容的規格要求。

有些情況下,暫時(shí)沒(méi)有合適的電阻和電容值,因此工程師必須確定是否能使用其他值。在 ADIsimPLL 的"工具"菜單中隱藏了一項小功能,稱(chēng)為"BUILT"。該功能可將電阻和電容值轉換為最接近的標準工程值,允許設計人員返回仿真界面,驗證相位裕量和環(huán)路帶寬的新數值。

寄存器

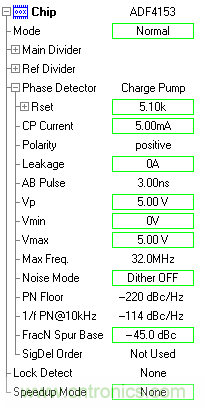

ADI PLL 提供很多用戶(hù)可配置選項,具有靈活的設計環(huán)境,但也會(huì )產(chǎn)生如何確定存儲在每個(gè)寄存器中數值的難題。一種方便的解決方案是使用評估軟件設置寄存器值,甚至 PCB 未連接仿真器時(shí)也能這么做。然后,設置文件可保存為.stp 文件,或下載至評估板中。圖 1 顯示 ADIsimPLL 仿真結果,提供諸如VCO 內核電流等參數的建議寄存器值。

圖 1. ADIsimPLL 仿真軟件提供寄存器設置的建議值

原理圖和 PCB 布局

設計完整 PLL 電路時(shí),需牢記幾點(diǎn)。首先,重要的是匹配 PLL的參考輸入端口阻抗,將反射降至最低。另外,保持電容與輸入端口并聯(lián)組合值盡量小,因為它會(huì )降低輸入信號的壓擺率,增加 PLL 環(huán)路噪聲。更多詳細信息請參考 PLL 數據手冊上的輸入要求。

其次,將模擬電源與數字電源相分離,最大程度減少它們之間的干擾。VCO 電源特別敏感,因此此處的雜散和噪聲可輕易耦合至 PLL 輸出。更多注意事項以及詳細信息,請參考利用低噪聲 LDO 調節器為小數 N 分頻壓控振蕩器(VCO)供源,以降低相位噪聲 (CN-0147)

再則,用于組成環(huán)路濾波器的電阻和電容應當放置在盡可能離PLL 芯片近的地方,并使用仿真文件中的建議值。若您在改變環(huán)路濾波器元器件值之后發(fā)現難以鎖定信號,請嘗試使用最初用于評估板的數值。

對于 PCB 布局而言,其主要原則是將輸入與輸出分離,確保數字電路不會(huì )干擾模擬電路。例如,若 SPI 總線(xiàn)太過(guò)靠近參考輸入或 VCO 輸出,則訪(fǎng)問(wèn) PLL 寄存器時(shí),VCO 輸出會(huì )在 PLL輸出端產(chǎn)生雜散現象。

從熱設計角度來(lái)看,可在 PLL 芯片底下放置一個(gè)導熱接地焊盤(pán),確保熱量流經(jīng)焊盤(pán),到達 PCB 和散熱片。在極端環(huán)境下使用時(shí),設計人員應計算 PLL 芯片和 PCB 的所有熱參數。

有效利用 MUXOUT

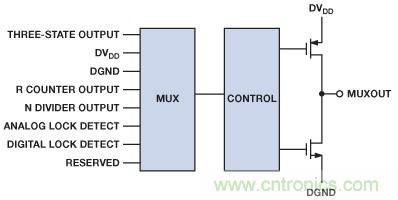

在調試階段開(kāi)始時(shí),若 PLL 不鎖定,則很難確定應當從何處開(kāi)始。第一步,可以使用 MUXOUT 查看是否所有內部功能單元都正常工作,如圖 2 所示。例如,MUXOUT 能顯示 R 計數器輸出,指示參考輸入信號良好,且寄存器內容成功寫(xiě)入。MUXOUT 還能檢查檢測器的鎖定狀態(tài),以及反饋環(huán)路中的 N分頻輸出。通過(guò)這種方法,設計人員可確定每個(gè)分頻器、增益或頻率值是否正確。這是調試 PLL 的基本過(guò)程。

圖 2. MUXOUT 引腳輔助 PLL 進(jìn)行調試

時(shí)域分析

調試 PLL 時(shí),使用時(shí)域分析,演示寫(xiě)入串行外設接口(SPI)總線(xiàn)上的寄存器數據是正確的。雖然讀寫(xiě)操作需要的時(shí)間比較長(cháng),但請確保 SPI 時(shí)序符合規格,且不同線(xiàn)路之間的串擾減小到最低程度。

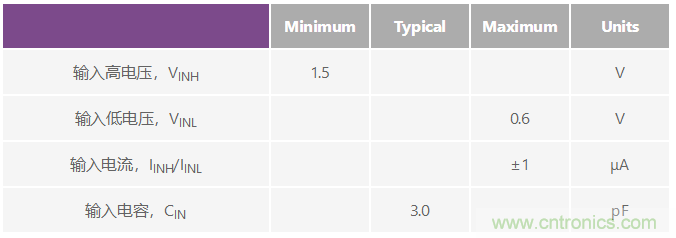

應當參考 PLL 數據手冊中的時(shí)序圖,以便確定數據建立時(shí)間、時(shí)鐘速度、脈沖寬度和其他規格。確保留有足夠的裕量,以便在所有條件下都滿(mǎn)足時(shí)序要求。使用示波器檢查時(shí)域內的時(shí)鐘和數據邊沿位于正確位置。若時(shí)鐘和數據線(xiàn)路太過(guò)接近,則串擾會(huì )使時(shí)鐘能量通過(guò) PCB 布線(xiàn)耦合至數據線(xiàn)路。這種耦合會(huì )導致數據線(xiàn)路在時(shí)鐘的上升沿產(chǎn)生毛刺。因此,讀寫(xiě)寄存器時(shí)需檢查這兩條線(xiàn)路,尤其當寄存器出現錯誤時(shí)。確保線(xiàn)路電壓滿(mǎn)足表 2 的規格。

表 2. 邏輯輸入

頻譜分析

頻域中的問(wèn)題更常見(jiàn)、更復雜。如果使用頻譜分析儀,則應當首先檢查 PLL 輸出是否鎖定;如果波形具有穩定的頻率峰值則表示鎖定。如果未鎖定,則應當遵循前文所述的步驟。

如果 PLL 已鎖定,則收窄頻譜分析儀帶寬,以便確定相位噪聲是否位于可接受范圍內,并將測試結果與仿真結果對照確認。測量某些帶寬條件下的相位噪聲,如 1 kHz、10 kHz 和 1 MHz。

若結果與預期不符,則應首先回顧環(huán)路濾波器設計,檢查 PCB板上元器件的真實(shí)值。然后,檢查參考輸入的相位噪聲是否與仿真結果一致。PLL 仿真相位噪聲應與真實(shí)值接近,除非外部條件有所不同,或向寄存器寫(xiě)入了錯誤值。

電源噪聲不可忽略,哪怕使用了低噪聲 LDO;因為 DC-DC 轉換器和 LDO 都可能成為噪聲源。LDO 數據手冊顯示的噪聲頻譜密度通常會(huì )影響噪聲敏感型器件,比如 PLL(見(jiàn)圖 3)。為PLL選擇低噪聲電源,特別是需要為VCO的內核電流提供電源。

圖 3. LDO 噪聲頻譜密度

通常 PLL 的輸出端會(huì )有四種類(lèi)型的雜散:PFD 或參考雜散、小數雜散、整數邊界雜散以及外部來(lái)源雜散,如電源。所有PLL 都至少有一種類(lèi)型的雜散,雖然永遠無(wú)法消除這些雜散,但某些情況下,在不同類(lèi)型的雜散或頻率之間進(jìn)行取舍,可以改進(jìn)整體性能。

若要避免參考雜散,請檢查參考信號的上升沿。邊沿過(guò)快或邊沿幅度過(guò)大都會(huì )對頻域造成嚴重的諧波現象。另外,仔細檢查PCB 布局,避免輸入和輸出之間產(chǎn)生串擾。

如需最大程度地減少小數雜散,可增加擾動(dòng),迫使小數雜散進(jìn)入本底噪聲中,但這樣做會(huì )略為增加本底噪聲。

整數邊界雜散不常見(jiàn),且僅當輸出頻率過(guò)于接近參考頻率的整數倍時(shí)才會(huì )發(fā)生,此時(shí)環(huán)路濾波器無(wú)法將其濾除。解決該問(wèn)題的簡(jiǎn)便方法是重新調節參考頻率方案。例如,若邊界雜散發(fā)生在 1100 MHz 處,且輸出為 1100.1 MHz,參考輸入為 20 MHz,則使用 100 kHz 環(huán)路濾波器將參考頻率改為 30 MHz 即可消除該雜散。

結論

調試 PLL 要求對 PLL 具有深入的理解,并且如果在設計階段格外仔細,就能避免很多問(wèn)題。若問(wèn)題發(fā)生在調試階段,請遵循本文所述之建議,對問(wèn)題逐一進(jìn)行分析并逐步解決問(wèn)題。更多信息,請參考網(wǎng)站上的豐富信息資源:www.analog.com/pll.

參考電路

Curtin, Mike, and Paul O’Brien.“Phase-Locked Loops for High-Frequency Receivers and Transmitters—Part 1.” Analog Dialogue, Volume 33, Number 1, 1999.

Curtin, Mike, and Paul O’Brien. “Phase-Locked Loops for High-Frequency Receivers and Transmitters—Part 2.” Analog Dialogue, Volume 33, Number 1, 1999.

Curtin, Mike, and Paul O’Brien, “Phase-Locked Loops for High-Frequency Receivers and Transmitters—Part 3.” Analog Dialogue, Volume 33, Number 1, 1999.

CN0147 Circuit Note. Powering a Fractional-N Voltage Controlled Oscillator (VCO) with Low Noise LDO Regulators for Reduced Phase Noise.

Fox, Adrian. “PLL Synthesizers (Ask the Applications Engineer—30).” Analog Dialogue, Volume 36, Number 3, 2002.

MT-086 Tutorial. Fundamentals of Phase-Locked Loops (PLLs).

推薦閱讀: