【導讀】石英晶體的外殼上標有器件的額定工作頻率,但那只是一個(gè)近似值,實(shí)際上晶體有多個(gè)諧振頻率,即使在理想情況下也是如此。本文以理想晶體的等效電路為例,表明并聯(lián)諧振頻率絕不會(huì )低于串聯(lián)諧振頻率。至于哪個(gè)諧振更重要,則取決于應用。

石英晶體的外殼上標有器件的額定工作頻率,但那只是一個(gè)近似值,實(shí)際上晶體有多個(gè)諧振頻率,即使在理想情況下也是如此。

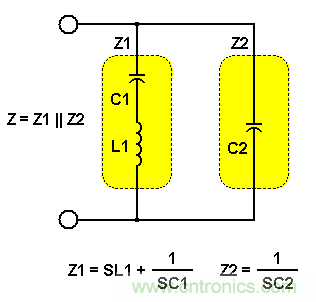

圖1顯示了理想晶體的等效電路,其中只有三個(gè)電路元件,串聯(lián)的電容C1和電感L1、與該L1 C1串聯(lián)對并聯(lián)的另一個(gè)電容C2。

圖1:理想石英晶體的等效電路。

在特定的串聯(lián)諧振頻率,輸入阻抗Z為零,L1和C1處于串聯(lián)諧振。電容C2與此無(wú)關(guān)。

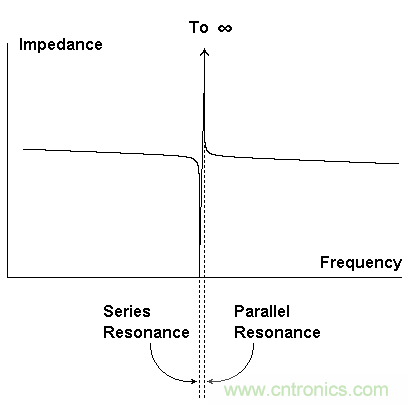

然而,在特定的并聯(lián)諧振頻率,輸入阻抗Z達到無(wú)窮大。這是C2與L1 C1的串聯(lián)組合發(fā)生并聯(lián)諧振的頻率,呈現電感性阻抗。要使L1 C1對在并聯(lián)諧振時(shí)呈現感性,并聯(lián)諧振必須發(fā)生在比串聯(lián)諧振更高的頻率。

因此,并聯(lián)諧振頻率只能比串聯(lián)諧振頻率高,即使只高一點(diǎn)點(diǎn)。并聯(lián)諧振頻率絕不會(huì )低于串聯(lián)諧振頻率。至于哪個(gè)諧振對你更重要,則取決于應用。

借助不復雜的數學(xué)運算,阻抗Z可以表示如下:

圖2:阻抗公式。

串聯(lián)諧振頻率:Fseries = 1/(2 * pi * sqrt(L1 C1))

并聯(lián)諧振頻率:Fparallel = 1/(2 * pi * sqrt(L1 C1 C2 /(C1 + C2)))

圖3:串聯(lián)和并聯(lián)諧振的相對位置。

本文轉載自電子技術(shù)設計。

推薦閱讀: