【導讀】本文中,我們將介紹先進(jìn)的掃描陣列雷達,從經(jīng)驗豐富的雷達信號處理專(zhuān)家的角度以及傳統的嵌入式系統設計人員的角度來(lái)研究其體系結構。

主動(dòng)電掃描陣列 (AESA) 雷達是當今先進(jìn)武器系統的關(guān)鍵組成 , 特別是機載作戰系統。而其體系結構的未來(lái)發(fā)展將超越最初的軍事應用,延伸到地球物理測繪、汽車(chē)輔助駕駛、自動(dòng)車(chē)輛、工業(yè)機器人和增強現實(shí)等領(lǐng)域:實(shí)際上, 這包括任何需要對大量的傳感器數據進(jìn)行調理,融合到模型中進(jìn)行判決的應用。

隨著(zhù) AESA 體系結構的擴展 , 它們將突破雷達信號處理專(zhuān)業(yè)應用 , 延伸到其他應用中。在外部應用中,這些設計會(huì )遇到典型的嵌入式設計流程:以 CPU 和軟件為中心的,基于 C 的以及與硬件無(wú)關(guān)的。本文中,我們將介紹先進(jìn)的掃描陣列雷達,從經(jīng)驗豐富的雷達信號處理專(zhuān)家的角度以及傳統的嵌入式系統設計人員的角度來(lái)研究其體系結構。

典型系統的角色

掃描陣列和傳統移動(dòng)盤(pán)式雷達的不同在于天線(xiàn)。掃描陣列并沒(méi)有采用熟悉的連續旋轉拋物線(xiàn)天線(xiàn),而是在大部分系統中采用了平面靜止天線(xiàn)。陣列并不是有一個(gè)單元聚 焦在反射器上,而是有數百上千個(gè)單元,每個(gè)單元都有自己的收發(fā)器模塊。系統電子電路處理每一單元信號的振幅和相位 , 形成雷達波束和接收方向圖并聚焦 , 設置定義總天線(xiàn)方向圖的干涉方向圖。

這一方法避免了采用大量的移動(dòng)部件,支持雷達實(shí)現傳統天線(xiàn)采用物理方法無(wú)法獲得的功能,例如,瞬 時(shí)改變波束方向,發(fā)送和接收同時(shí)有多個(gè)天線(xiàn)方向圖,或者把陣列分成多個(gè)天線(xiàn)陣,完成多項功能 —— 也就是,根據地形搜索目標,同時(shí)跟蹤目標。這些方法只需要在發(fā)送器增加一些信號,在每一接收器將信號分開(kāi)。重疊是一種很好的方法。

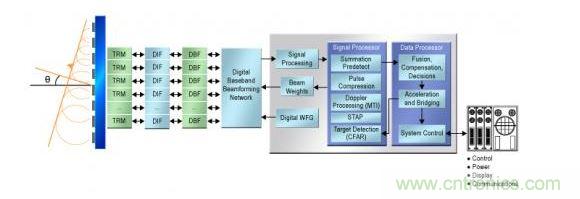

一個(gè)完整的系統從CPU簇傳輸到天線(xiàn),然后再返回 ( 圖 1 ) 。 一開(kāi)始處理時(shí),軟件控制的波形發(fā)生器產(chǎn)生系統要發(fā)送的啁啾。取決于應用,降噪、多普勒處理和隱身的需求會(huì )對信號有所損傷。

圖 1 .一個(gè)非常簡(jiǎn)化的 AESA 系統結構圖。

波形發(fā)生器將信號送到聚束網(wǎng)絡(luò )中。在這里,信號被連接至每一發(fā)送通道。在這一級,數字復用器在通道上應用振幅權重來(lái)實(shí)現空間濾波,對波形整形。這一步也可以 稍后再做。在很多設計中,每一通道的信號現在會(huì )通過(guò)一個(gè)數模轉換器 (DAC) ,然后輸入到模擬 IF 和 RF 上變頻器中。 RF 上變頻后,信號到達獨立的發(fā)送器模塊,附加上相移或者時(shí)延,調整振幅 ( 如果在基帶沒(méi)有做 ) ,最終進(jìn)行濾波和放大。

一開(kāi)始,接收到的信號實(shí)際上通過(guò)與反方向相同的通路,在后端要進(jìn)行更多的處理。在每一個(gè)天線(xiàn)單元,限幅器和帶通濾波器保護了低噪聲放大器。放大器驅動(dòng) RF 下變頻器,可以結合模擬放大和調相功能。信號從 IF 級傳輸到基帶,每一天線(xiàn)單元的信號到達其模數轉換器 (ADC) 。然后,聚束模塊把天線(xiàn)信號重新組合成一路或者多路復數數據采樣流,每一數據流代表了來(lái)自某一接收波束的信號。這些信號流通過(guò)大占空比的數字信號處理 (DSP) 電路,進(jìn)一步調理數據,進(jìn)行多普勒處理,嘗試從噪聲中提取出實(shí)際信號。

[page]

什么時(shí)候進(jìn)行數據轉換

在很多設計中,大部分信號處理工作是以模擬方式完成的。但是,隨著(zhù)數字速度的提高,功耗和成本的降低,數據轉換器與天線(xiàn)靠的越來(lái)越近。 Altera 應用專(zhuān)家 Colman Cheung 建議了一個(gè)理想的系統,直接從 DAC 驅動(dòng)天線(xiàn)單元。但是, 2013 年,這類(lèi)設計在技術(shù)上還無(wú)法實(shí)現,特別是, trans-GHz RF 。

目前可以把數據轉換器放在 IF 中,進(jìn)行 IF 頻率轉換,所有基帶處理工作都是數字化的 ( 圖 2 ) 。 可以在基帶聚束網(wǎng)絡(luò )中,以數字方式在天線(xiàn)單元之間產(chǎn)生干涉方向圖的時(shí)延,每一個(gè)天線(xiàn)單元并不需要模擬相移器或者延時(shí)線(xiàn)。這種劃分方法支持 DSP 設計人員把發(fā)送和接收通路分解成分立的功能 —— 乘法器、濾波器、用于延時(shí)的 FIFO ,以及加法器,在 MATLAB 中對其進(jìn)行建模,從庫中實(shí)現它們??梢园岩笞羁量痰墓δ芊诺綄?zhuān)門(mén)開(kāi)發(fā)的 ASIC 、 FPGA 或者 GPU 芯片中,而把要求不太高的運算分組成 DSP 芯片或者加速器中的代碼。

圖 2 .把數據轉換器放到 IF 級的最后。

需要特別注意信號從聚束網(wǎng)絡(luò )出來(lái)后的接收鏈信號處理 , 這是因為其存儲器和處理需求會(huì )非常大 , 涉及到的動(dòng)態(tài)范圍非常寬 —— 從干擾發(fā)射器輸入到搜索探測范圍的每一邊沿。會(huì )需要高精度浮點(diǎn)硬件,還需要更強的處理能力。

在其最后級,有目的的對接收鏈進(jìn)行修改并實(shí)現。通過(guò)其濾波、聚束和脈沖壓縮級,鏈的任務(wù)是從噪聲中提取出信號,特別是那些可能承載了環(huán)境中實(shí)際目標信息的信號。然后,重點(diǎn)從信號轉向它們所代表的目標,任務(wù)的本質(zhì)發(fā)生了改變。

從信號到目標

脈沖壓縮是這一抽象過(guò)程的開(kāi)始。在時(shí)間域或者頻域,脈沖壓縮器一般通過(guò)自相關(guān)找到有可能含有發(fā)送啁啾的波形。然后,它采用脈沖目標來(lái)表示這些波形 —— 含有到達時(shí)間、頻率和相位以及其他相關(guān)數據的數據包。從這里開(kāi)始,接收鏈會(huì )處理這一數據包而不是接收到的信號。

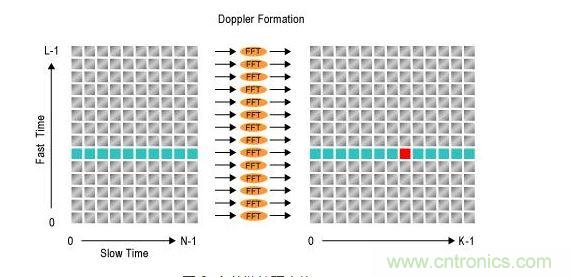

下 一步一般是多普勒處理。首先,脈沖被送入方格陣列中( 圖 3 ) 。在陣列中,每一列含有從某一發(fā)射器啁啾返回的脈沖。陣列中會(huì )有很多列,這取決于系統能夠承受多大的延時(shí)。陣列中的行表示返回切換時(shí)間:距離陣列的 x 軸越遠,發(fā)射器啁啾和接收脈沖到達時(shí)間之間的延時(shí)就越大。這樣,延時(shí)方格也代表了與某一脈沖反射的目標的距離。

圖 3 .多普勒處理方格。

把一系列啁啾脈沖置入到正確的方格中后 , 多普勒處理程序水平移動(dòng)數據 —— 觀(guān)察從一個(gè)目標返回的脈沖隨時(shí)間的變化 , 提取出相對速度和目標頭部信息。這一處理方法需要很大的環(huán)形緩沖,無(wú)論某一多普勒算法一次能夠處理多少方格,緩沖都能夠容納所有的方格。

[page]

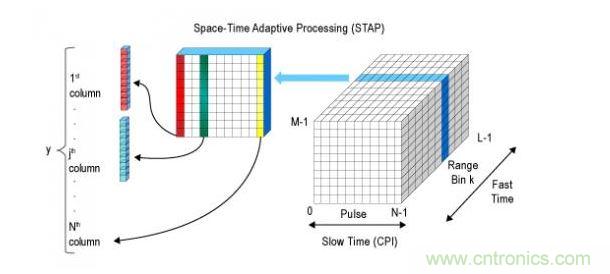

先進(jìn)系統在陣列中增加了另一個(gè)維度。通過(guò)把天線(xiàn)劃分成子陣列,系統可以同時(shí)發(fā)送多個(gè)波束,然后,使用相同的多旁瓣天線(xiàn)方向圖設置接收器進(jìn)行監聽(tīng)?;蛘?,系統 通過(guò)聚束或者使用合成孔徑方法來(lái)掃描波束?,F在,當裝入壓縮后的脈沖時(shí),系統建立一個(gè)三維方格陣列:一個(gè)軸上是發(fā)送脈沖,第二個(gè)是返回延時(shí),第三個(gè)是波束 方位( 圖 4 ) ?,F在,對于每一路脈沖,我們有兩維或者三維方格陣列,同時(shí)表示距離和方向 —— 表示物理空間。這種存儲器的排列是空時(shí)自適應處理 (STAP) 的起點(diǎn)。

圖 4 .多維方格為STAP建立矩陣。

這一術(shù)語(yǔ)可以解釋為 :“ 空時(shí)” , 數據組在 3D 空間統一了目標的位置 , 含有與目標相關(guān)的啁啾時(shí)間。之所以是“自適應”,是因為算法從數據中獲得自適應濾波。

概 念上,實(shí)際情況也是如此,構成自適應濾波器是一個(gè)矩陣求逆過(guò)程:這一數據要與哪一矩陣相乘,得到噪聲中隱藏的結果 ? 據Altera資深技術(shù)營(yíng)銷(xiāo)經(jīng)理Michael Parker,推測的隱藏方向圖信息可能來(lái)自多普勒處理過(guò)程發(fā)現的種子,從其他傳感器采集的數據,或者來(lái)自智能數據。運行在 CPU 下游的算法把假設的方向圖插入到矩陣方程中,解出能夠產(chǎn)生預期數據的濾波函數。

很顯然,在這一點(diǎn),計算負載非常大。反變換算法需要的動(dòng) 態(tài)范圍要求進(jìn)行浮點(diǎn)計算。對于戰斗環(huán)境中一個(gè)實(shí)際的中等規模系統,必須實(shí)時(shí)進(jìn)行處理,Parker估算了STAP負載會(huì )達到幾個(gè) TFLOPS 。在采用了低分辨率、窄動(dòng)態(tài)范圍的系統中,實(shí)時(shí)性要求并不高,例如,簡(jiǎn)單的汽車(chē)輔助駕駛系統或者合成孔徑映射系統等,這一負載會(huì )顯著(zhù)減小。

從 STAP ,信息進(jìn)入到通用CPU中,復雜但是數字計算量小,軟件嘗試對目標進(jìn)行分類(lèi),構建環(huán)境模型,估算威脅所在,或者告訴操作員,或者直接采取緊急措施。在這一點(diǎn),我們不但在信號處理域處理信號,而且還進(jìn)入了人工智能領(lǐng)域。

[page]

兩種體系結構

從一名經(jīng)驗豐富的雷達系統設計師的角度看,我們還只是膚淺的了解了 AESA 戰斗雷達。這一參考方法把網(wǎng)絡(luò )看成是相對靜態(tài)的 DSP 鏈,都連接至STA 模塊,其本身是軟件受控的矩陣算術(shù)單元。除此之外,從 DSP 專(zhuān)家的角度看,是一組 CPU 內核。

作為對比,汽車(chē)或者機器人系統設計人員會(huì )從完全不同的角度看系統。從嵌入式設計人員的角度看,系統只是一大段軟件,有一些非常專(zhuān)用的 I/O 器件,以及需要進(jìn)行加速的某些任務(wù)。有經(jīng)驗的雷達信號工程師考慮到信號處理和通用硬件的相對規模,可能會(huì )對這一方法不屑一顧。很顯然,機載多功能雷達的數 據速率、靈活性和動(dòng)態(tài)范圍要求采用專(zhuān)用 DSP 流水線(xiàn)以及大量的本地緩沖才能完成實(shí)時(shí)處理。但是對于有幾個(gè)天線(xiàn)單元的不同應用,簡(jiǎn)單的環(huán)境、更短的距離和較低的分辨率,以 CPU 為中心的觀(guān)點(diǎn)帶來(lái)了一些有意思的問(wèn)題。

萊斯大學(xué)的 Gene Frantz 教授提出的第一個(gè)問(wèn)題是,定義真實(shí)環(huán)境的 I/O 。第二個(gè)問(wèn)題是選擇 CPU 。 Frantz 注意到,“很少只有一個(gè) CPU 。更常見(jiàn)的是異構多處理系統。” Frantz 建議這一方法不從 MATLAB 中的 DSP 函數開(kāi)始,而是從 C 語(yǔ)言中描述的完整系統開(kāi)始。然后,以 CPU 為中心的設計人員不是定義設計中 DSP 和 CPU 域之間的硬件邊界,而是“不斷優(yōu)化并加速 C 代碼。”

實(shí)際結果可能與以 DSP 為中心的方法完全不同。例如,以 CPU 為中心的方法一開(kāi)始假設在一片通用 CPU 上執行所有工作。如果速度不夠快,這一方法轉向多片 CPU ,共享一個(gè)分層的連續存儲器。只有當多核不足以完成任務(wù)時(shí),這一方法才轉向優(yōu)化的硬件加速器。

相似的,以 CPU 為中心的設計從假設一個(gè)統一的存儲器開(kāi)始。它為每一個(gè)處理器分配連續高速緩存,為加速器分配本地工作存儲器。它開(kāi)始時(shí)并不假設任何硬件流水線(xiàn),也不把任務(wù)混合映射到硬件資源上。

在要求最嚴格的應用中,同一個(gè)系統設計可能會(huì )同時(shí)采用兩種體系結構方法。幾乎每一任務(wù)嚴格的帶寬和計算需求都導致采用專(zhuān)用硬件流水線(xiàn)和存儲器例化。要求大幅度降低功耗可能會(huì )迫使做出采用高精度數字方法的決定,這使得在任務(wù)之間共享硬件變得越來(lái)越復雜。

精度是 Frantz 強調的一點(diǎn)。他指出,“把有效位數減少一半使您能夠將性能提高一個(gè)量級。”為降低功耗,您可以對以上這些做出犧牲或者部分犧牲。

Frantz 指出了關(guān)于模擬 / 數字邊界的問(wèn)題。他說(shuō):“我們需要重新考慮模擬信號處理。三十年以前,我們開(kāi)始告訴系統設計人員只要做好數據轉換就行,我們采用數字方法完成其他所有工 作。但是實(shí)際上,在 8 位分辨率,模擬和數字方法大概是相同的。模擬是不是更好一些 ? 這取決于在您的系統中,‘更好''的含義是什么。”

地 球物理測繪或者自動(dòng)陸地車(chē)輛系統使用的合成孔徑雷達等窄帶系統會(huì )采用與戰斗雷達完全不同的體系結構。它可以使用模擬濾波器、上變頻器 / 下變頻器以及聚束功能來(lái)完成一個(gè)寬帶存儲器系統的所有后續處理工作,還使用具有浮點(diǎn)加速器和動(dòng)態(tài)負載均衡功能的多個(gè)異構處理器 ( 圖 5 ) 。

圖 5 .一個(gè)理想的低性能AESA系統。

對信號處理任務(wù)進(jìn)行可視化處理 , 使其在軟件中完成 , 系統設計人員獲得了新的運行時(shí)選擇 , 例如 , 在任務(wù)之間移動(dòng)處理資源 , 關(guān)斷不需要的處理器 , 盡早修改算法 ,以便響應數據碼型 , 或者運行多種算法 , 查看哪一種能夠得出最佳結果。

AESA 雷達系統不但為研究實(shí)現策略提供了豐富的環(huán)境,而且還提供了方法來(lái)研究有大量信號的系統。這些有源陣列分布在軍事等多種設計應用中,所以,不應該局限在傳 統的嵌入式設計思路中。因此,對于完全不同的需要大量信號的領(lǐng)域要有新思路,這包括信號智能和網(wǎng)絡(luò )安全等應用。這是值得注意的領(lǐng)域。