【導讀】設計一個(gè)要求高通道密度的系統時(shí),例如在測試儀器儀表中,電路板上通常需要包括大量開(kāi)關(guān)。當使用并行接口控制的開(kāi)關(guān)時(shí),控制開(kāi)關(guān)所需的邏輯線(xiàn)路以及用于生成GPIO控制信號的串行轉并行轉換器會(huì )占用很大比例的板空間。

本文討論旨在解決這種設計挑戰的ADI公司新一代SPI控制開(kāi)關(guān)及其架構,以及相對于并行控制開(kāi)關(guān),它在提高通道密度上有何優(yōu)勢。ADI公司創(chuàng )新的多芯片封裝工藝使得新型SPI轉并行轉換器芯片可以與現有高性能模擬開(kāi)關(guān)芯片結合在同一封裝中。這樣既可節省空間,又不會(huì )影響精密開(kāi)關(guān)性能。

測試設備中的通道數最大化至關(guān)重要,因為通道越多,可以并行測試的器件就越多,進(jìn)而壓縮最終客戶(hù)的測試時(shí)間和成本。測試儀通過(guò)開(kāi)關(guān)來(lái)分享其資源以支持多個(gè)被測器件 (DUT),故開(kāi)關(guān)是增加通道數的關(guān)鍵元件。但是,并行控制的開(kāi)關(guān)數量越多,控制線(xiàn)路也就越多,占用的電路板空間相應地增加,這嚴重制約了可以實(shí)現的通道密度。

在此情況下,使用SPI控制的開(kāi)關(guān)在解決方案尺寸和通道數方面具有顯著(zhù)的優(yōu)勢。SPI開(kāi)關(guān)可以采用菊花鏈形式布置,相比于傳統解決方案,此舉可大幅減少所需的數字線(xiàn)路數。

本文將詳細說(shuō)明通道數最大化過(guò)程中會(huì )遇到的問(wèn)題,討論用于控制一組開(kāi)關(guān)的傳統方法及其缺點(diǎn),提出SPI控制的模擬開(kāi)關(guān)解決方案,最后介紹同類(lèi)產(chǎn)品中性能最佳的ADI SPI控制精密開(kāi)關(guān)。

通道數最大化的常見(jiàn)問(wèn)題

當模塊開(kāi)發(fā)的主要目標是通道數最大化時(shí),板空間就會(huì )變得很珍貴。開(kāi)關(guān)是提高系統通道數的關(guān)鍵,但隨著(zhù)開(kāi)關(guān)數目增加,開(kāi)關(guān)本身、邏輯線(xiàn)路及生成這些邏輯信號所需的器件會(huì )占用大量板空間,使可用空間減少。最終,受制于控制開(kāi)關(guān)本身所需的相關(guān)因素,只能實(shí)現很有限的通道數。

傳統并行開(kāi)關(guān)解決方案

提高通道密度的最常見(jiàn)解決方案是使用由并行邏輯信號控制的開(kāi)關(guān)。這需要大量GPIO信號,標準微控制器無(wú)法提供如此多的信號。為了生成GPIO信號,一種解決辦法是使用串行轉并行轉換器。這些器件輸出并行信號,并由I2C和SPI等串行協(xié)議進(jìn)行配置。

圖1中的布局顯示了8個(gè)ADG1412 四通道、單刀單擲(SPST)開(kāi)關(guān),采用4 x 8交叉點(diǎn)配置,位于一個(gè)6層板上。這些開(kāi)關(guān)由兩個(gè)串行轉并行轉換器控制,串行線(xiàn)路來(lái)自一個(gè)控制板。每個(gè)轉換器提供16條GPIO線(xiàn)路,這些線(xiàn)路分布到8個(gè)開(kāi)關(guān)。布局顯示了器件、電源去耦電容和數字控制信號(灰色)的占地大小。采用并行控制開(kāi)關(guān)的4 x 8矩陣解決方案的尺寸為35.6 mm x 19 mm,占用面積為676.4 mm2。

圖1.并行控制開(kāi)關(guān)4 x 8矩陣布局

從圖1可以明顯看出,很大比例的面積被串行轉并行轉換器和數字控制線(xiàn)路占用,而不是被開(kāi)關(guān)本身占用。對板空間的這種低效使用是很糟糕的,會(huì )大幅減少模塊中的開(kāi)關(guān)數目,進(jìn)而影響系統通道數。

SPI開(kāi)關(guān)解決方案

圖2顯示了一個(gè)4 x 8交叉點(diǎn)配置,8個(gè)四通道SPST開(kāi)關(guān)位于一個(gè)6層板上。不過(guò),這次開(kāi)關(guān)是SPI控制的ADGS1412器件。像之前一樣,圖中顯示了器件尺寸、電源去耦電容和SDO上拉電阻。

該解決方案展示器件以菊花鏈形式配置。所有器件共享來(lái)自SPI接口的片選和串行時(shí)鐘數字線(xiàn)路,菊花鏈中的第一個(gè)器件接收串行數據。然后,該數據被傳送至鏈(像一個(gè)移位寄存器)中的所有器件。這個(gè)示例解決方案的尺寸是30 mm x 18 mm,面積為540 mm2。

以菊花鏈形式使用SPI接口可大大減少串行轉并行轉換器和數字線(xiàn)路占用的板空間。采用這種開(kāi)關(guān)配置,總電路板面積可減少20%,這使得通道密度大大提高。系統平臺也得到了簡(jiǎn)化。當電路板上的開(kāi)關(guān)數目提高時(shí),節省的面積隨之增加,包含數百個(gè)開(kāi)關(guān)的電路板可節省50%以上的空間。

這說(shuō)明在更小的面積中可以放入更多開(kāi)關(guān),相比于傳統串行轉并行轉換器方案,同樣面積的電路板將能支持更多通道。

圖2.菊花鏈開(kāi)關(guān)4 x 8矩陣布局

圖3.SPI開(kāi)關(guān)和并行開(kāi)關(guān)解決方案的面積對比

ADI SPI開(kāi)關(guān)特性

ADI公司的新型SPI開(kāi)關(guān)系列可用來(lái)實(shí)現更高通道密度,如上例所示。通過(guò)創(chuàng )新的堆疊式雙芯片解決方案(圖4),ADI公司目前業(yè)界領(lǐng)先的精密開(kāi)關(guān)可以利用工業(yè)標準SPI模式0接口進(jìn)行配置。這意味著(zhù)不僅可以節省空間,而且不會(huì )對系統性能造成不利影響。下面是ADI新型SPI開(kāi)關(guān)的主要功能總結。

圖4.ADI公司創(chuàng )新堆疊式雙芯片解決方案

菊花鏈模式

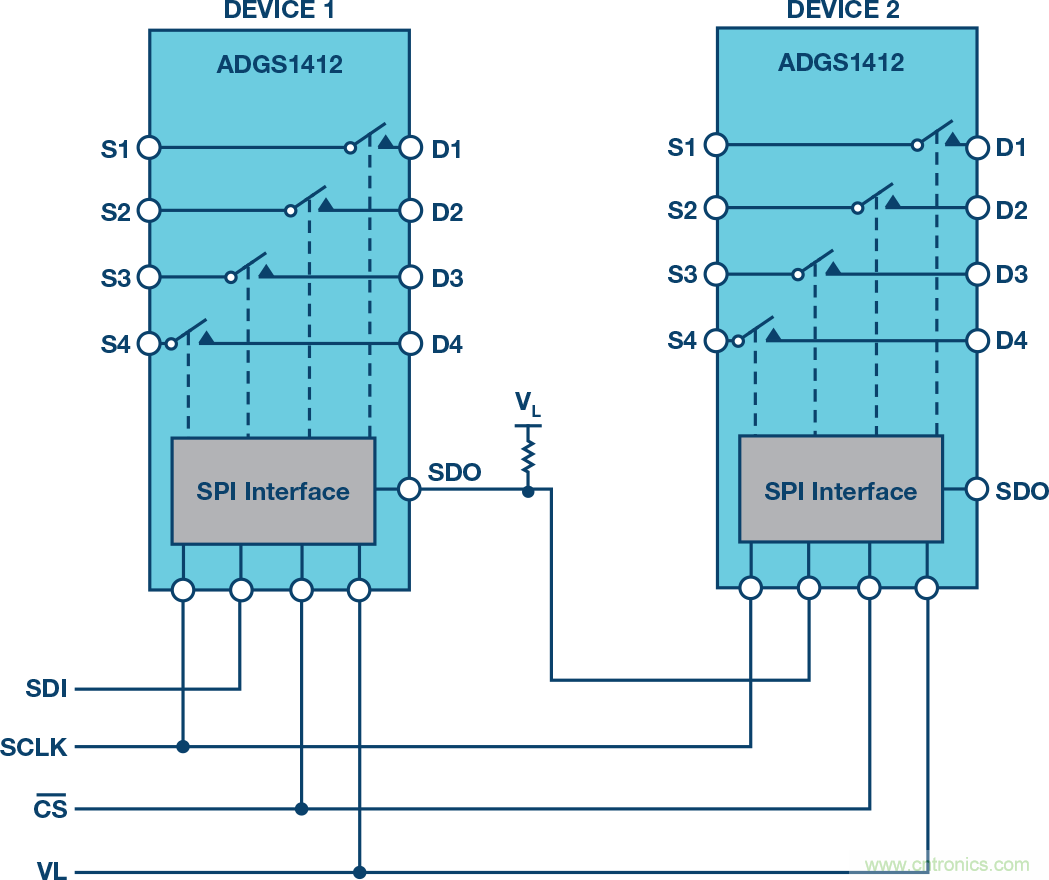

如上所述,ADI SPI開(kāi)關(guān)能以菊花鏈模式工作。采用菊花鏈配置的ADGS1412器件連接如圖5所示。所有器件共享CS 和SCLK數字線(xiàn)路,而器件的SDO與下一器件的SDI形成連接。利用單個(gè)16位SPI幀指令菊花鏈中的所有器件進(jìn)入菊花鏈模式。在菊花鏈模式下,SDO是SDI的8周期延遲版本,故期望的開(kāi)關(guān)配置可以從菊花鏈中的一個(gè)器件傳遞到另一個(gè)器件。

圖5.采用菊花鏈配置的兩個(gè)開(kāi)關(guān)

錯誤檢測功能

當器件處于尋址模式或突發(fā)模式時(shí),可以檢測SPI接口上的協(xié)議和通信錯誤。有三種錯誤檢測方法,分別是SCLK錯誤計數、無(wú)效讀取和寫(xiě)入地址以及最多3位的CRC錯誤檢測。這些錯誤檢測功能確保數字接口即使在惡劣環(huán)境下也能可靠工作。

ADI SPI開(kāi)關(guān)系列

ADGS1412是ADI公司正在開(kāi)發(fā)的SPI開(kāi)關(guān)系列中的首款產(chǎn)品。得益于A(yíng)DI公司開(kāi)發(fā)的創(chuàng )新雙芯片解決方案,ADGS1412不僅具有與并行控制器件ADG1412相同的同類(lèi)最佳的低RON性能,而且具備串行接口帶來(lái)的優(yōu)勢。

該系列將以ADI公司的高性能開(kāi)關(guān)為基礎構建,提供現有、業(yè)界領(lǐng)先的開(kāi)關(guān)的SPI控制版本。表1列出了ADI新型SPI開(kāi)關(guān)系列當前和計劃發(fā)布的產(chǎn)品。產(chǎn)品型號代表何種模擬開(kāi)關(guān)芯片與SPI轉并行轉換器進(jìn)行多芯片封裝,附加的S表示其為SPI控制版本。這些產(chǎn)品將在2017年陸續發(fā)布。

表1.計劃中的新型SDI SPI器件優(yōu)化產(chǎn)品

結語(yǔ)

在高通道密度應用中,與使用并行控制開(kāi)關(guān)相比,使用SPI控制開(kāi)關(guān)有很多優(yōu)勢。它能減少每個(gè)開(kāi)關(guān)占用的電路板空間,進(jìn)而實(shí)現更高的開(kāi)關(guān)密度。這是因為它減少了所需的數字控制線(xiàn)路,并且不再需要其它器件來(lái)提供這些控制線(xiàn)路。

ADI公司的創(chuàng )新精密SPI開(kāi)關(guān)解決方案支持提高通道密度。這些器件提供的菊花鏈模式有利于實(shí)現上述目標。由于采用雙芯片解決方案,ADI公司當前開(kāi)關(guān)產(chǎn)品的業(yè)界領(lǐng)先開(kāi)關(guān)性能得以傳承到新產(chǎn)品。ADGS1412是新型SPI控制開(kāi)關(guān)系列中的首款產(chǎn)品,完整產(chǎn)品系列將于2017年和2018年陸續發(fā)布。

推薦閱讀: