【導讀】用計數法測出相位差,可實(shí)現對有效值0.5V~5V,頻率10Hz~100KHz 信號的相位差測量。系統功能由按鍵控制,可對測量結果實(shí)時(shí)顯示,人機交互界面友好,達到了較好的性能指標。那么多功能計數器系統如何設計呢?都有哪些主要板塊設計呢?

以單片機和 FPGA構成的最小系統為控制核心,由寬帶放大模塊,比較整形模塊,頻率、相位差測量模塊等模塊構成。在FPGA內采用等精度測頻法測出頻率和周期,可實(shí)現對有效值為0.005V~5V,頻率范圍1Hz~35MHz 信號的頻率、周期的測量。用計數法測出相位差,可實(shí)現對有效值0.5V~5V,頻率10Hz~100KHz 信號的相位差測量。系統功能由按鍵控制,可對測量結果實(shí)時(shí)顯示,人機交互界面友好,達到了較好的性能指標。

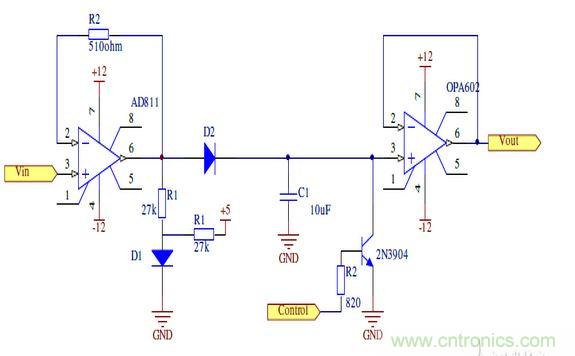

峰值檢波模塊

在進(jìn)入模擬開(kāi)關(guān)之前,需要進(jìn)行峰值檢波,通過(guò)測得的信號的幅值確定模擬開(kāi)關(guān)的通道。峰值檢波電路是由二極管電路和電壓跟隨器組成,其工作原理為:當輸入電壓正半周通過(guò)時(shí),檢波管D2導通,對電容C1充電,直到到達其峰值。三極管的基極由單片機控制,產(chǎn)生10us 的高電平使電容放電,以減少前一頻率測量對后一頻率測量的影響,提高幅值測量精度。其中D1處于常導通狀態(tài),用以補償D2 上造成的壓降。電容C1 的取值需根據被測信號的頻率合適的選取,此電路中的二極管使用高頻二極管,可大大提高測量范圍的頻率上限。其電路圖如圖2.2 所示。

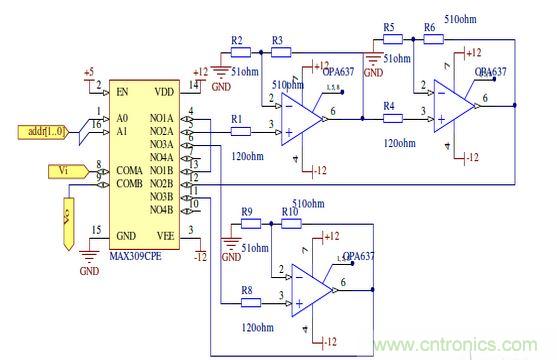

寬帶通道放大器分析

為了檢測有效值0.005V~ 5V的信號(即Vp_p 為0.014V~14V)的頻率,而高頻比較器TL3116能檢測到的輸入信號的最小幅度Vp_p=0.8V,因此需要對信號進(jìn)行程控放大。當測得的信號峰峰值Vp_p小于0.1V 時(shí),設定放大倍數為120,當0.1V~1V 時(shí)設定放大倍數為10,當Vp_p大于1V時(shí),設定放大倍數為1。以MAX309為模擬開(kāi)關(guān),用OPA637接成一級同相放大器進(jìn)行10倍增益放大。用兩級OPA637級聯(lián)進(jìn)行120倍放大。其原理圖如圖上。

[page]

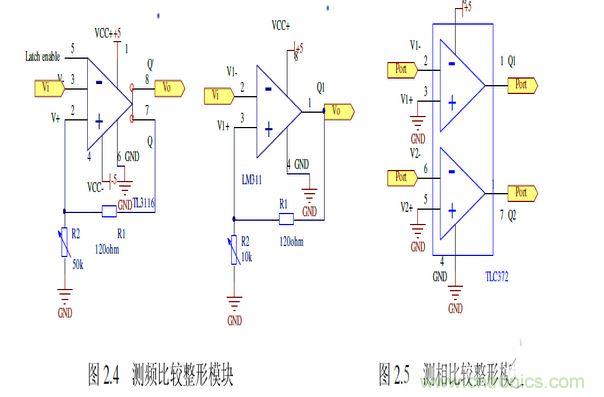

比較整形電路

在測頻、測周部分,由于我們沒(méi)有帶寬由1Hz 到35MHz 的比較器,所以采用分段處理的方法實(shí)現整個(gè)頻帶的測量,高頻部分用TI公司的TL3116實(shí)現,低頻部分采用LM311。為抑制干擾引起的誤翻轉,我們采取了帶正反饋的滯回比較電路的形式。

在反相輸入方式時(shí),其正向閾值電壓,對應比較后信號的下降沿。負向閾值電平為0V,對應于比較后信號的上升沿。故輸出信號的上升沿仍屬過(guò)零比較。測相的兩路信號經(jīng)過(guò)整形,要使產(chǎn)生的額外相差最小,必須保證兩路通道參數的一致性,選用TI 公司的雙路比較器TLC372。

FPGA 模塊

本系統采用數字方法在FPGA 內部進(jìn)行頻率和相位差的測量。其電路圖如圖2.6 所示。其中fx_h 和fx_l 分別為高頻信號和低頻信號輸入端。CH1 和CH2分別為兩路相位信號如數端。