【導讀】實(shí)現確定性延遲是當今許多系統設計中討論的主題。過(guò)去,人們一直在努力提高數據傳輸速度和帶寬。如今的應用則越來(lái)越重視確定性——即要求數據包在精確的、可重復的時(shí)間點(diǎn)傳送。

實(shí)現確定性延遲是當今許多系統設計中討論的主題。過(guò)去,人們一直在努力提高數據傳輸速度和帶寬。如今的應用則越來(lái)越重視確定性——即要求數據包在精確的、可重復的時(shí)間點(diǎn)傳送。

本文將在設備的層面討論確定性這一主題,以及如何設計超高速數據轉換和信號處理系統以保證確定性延遲。

以下三個(gè)因素將決定確定性如何實(shí)現:

1. 采取措施減少數字設計組件中發(fā)生的亞穩態(tài)事件

2. 計算數字后端的延遲,確保多個(gè)數據鏈路通道之間(如HSSL)的數據對齊

3. 優(yōu)化時(shí)間延遲的余量,保證不會(huì )因為 PVT 的變化而出現意外的不確定性。

具體來(lái)說(shuō),我們將考慮亞穩態(tài)的影響和同步系統的方案,并介紹如何在模擬和數字信號處理域之間的接口上保持確定性。

管理超高速系統中數據轉換器陣列的延遲的能力在復雜系統中非常重要,這些系統包括數字波束導向雷達、波束成形多載波通訊等。延遲會(huì )降低系統的性能。工程師的目標是將延遲控制在可知的范圍內。

術(shù)語(yǔ)表 術(shù)語(yǔ)表

●ADC – 模數轉換器

●CDC – 跨時(shí)鐘域

●CLK – 采樣時(shí)鐘

●CMU – 時(shí)鐘管理單元

●ESIstream – 高效串行接口

●ESS – ESIstream 同步序列

●FPGA –現場(chǎng)可編程邏輯門(mén)陣列

●GT – 千兆比特收發(fā)器

●HSSLs – 高速串行線(xiàn)路

●LD – 邏輯器件(如FPGA或ASIC)

●LMFC – 本地多幀時(shí)鐘

●MZ – 亞穩態(tài)域

●PVT – 過(guò)程、電壓和溫度

●SSO – 低速同步輸出

如今有兩種流行的 IC 數據接口:無(wú)許可證的 ESIstream 和行業(yè)標準JESD204B(sub-classes 1 和2)。這兩種接口都被廣泛應用于連接數據轉換器和邏輯器件(LD) 如 FPGA和 ASIC。兩者都承諾確定性,但在具體的實(shí)現上有所不同。本文將闡述,考慮到優(yōu)秀的靈活性、較低的開(kāi)銷(xiāo)和絕對延遲,ESIstream將是最佳的選擇。

延遲的定義

延遲的簡(jiǎn)單定義是操作和響應之間的時(shí)間差。在采樣數據系統中,通常我們最關(guān)心的是最大延遲。對于以硬件為重點(diǎn)的本文,不確定性的來(lái)源以及如何管理這些來(lái)源是一個(gè)關(guān)鍵問(wèn)題。確定性是一個(gè)簡(jiǎn)單的需求,即系統對于給定的一組輸入產(chǎn)生相同的結果。不論環(huán)境或啟動(dòng)條件如何變化,結果都是可預測的,并排除隨機因素。本質(zhì)上,確定性系統提供了有限的響應。

實(shí)現確定性行為的挑戰

不確定性的來(lái)源并不直觀(guān),特別是對于 GHz 的采樣頻率。圖 1 標出了單片 ADC EV12AQ600 連接到一個(gè)邏輯設備(LD)時(shí)的幾個(gè)源。不確定性是由亞穩態(tài)產(chǎn)生(參見(jiàn)側欄),這是同步邏輯系統引入的一個(gè)因素。除此之外,還有三個(gè)因素會(huì )加劇這種不確定性:

●跨時(shí)鐘域(CDC)導致潛在的不等長(cháng)的信號路徑,另外還有信號線(xiàn)的物理不等長(cháng)

●多個(gè) HSSL 之間的數據對齊導致的 LD 輸出緩沖區的延遲差異

●PVT(過(guò)程、電壓和溫度)的影響

亞穩態(tài)

亞穩態(tài)是同步系統在狀態(tài)轉換過(guò)程中由于有限的建立保持時(shí)間而產(chǎn)生的邏輯狀態(tài)的不確定性??赏ㄟ^(guò)創(chuàng )建從 MZ 回退的狀態(tài)采樣點(diǎn)避免亞穩態(tài)(圖5)。

圖 1 EV12AQ600 的不確定性源和積累延遲

跨時(shí)鐘域(CDC)

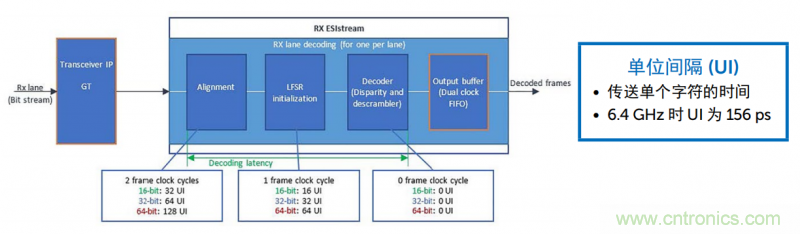

數據轉換器和附加的邏輯設備(這里是 FPGA)都是復雜的同步子系統,具有相關(guān)的分層時(shí)鐘架構,加強了本地的確定性。必須使用一個(gè)外部的低抖動(dòng)主時(shí)鐘來(lái)同步兩個(gè)域在 ADC 中,當使用雙時(shí)鐘 FIFO 將數據從編碼器時(shí)鐘域傳輸到發(fā)送器/串行化時(shí)鐘域時(shí),會(huì )產(chǎn)生可變延遲。在FPGA 中,當使用收發(fā)器緩沖將數據從接收器/反串行化器傳輸到解碼器,以及使用輸出緩沖將數據從解碼器傳輸到用戶(hù)應用時(shí),會(huì )產(chǎn)生可變延遲。EV12AQ600 的輸出數據通過(guò) 4 對 ESIstream 串行線(xiàn)傳輸。由于CDC 的緣故,每根線(xiàn)的延遲都略有不同。EV12AQ600 數據輸出端的每根線(xiàn)的延遲可在 126 到 142 個(gè)時(shí)鐘周期之間變化(32 個(gè)UI 的可變延遲)。此外,ADC 和接收解碼器之間的物理距離延遲了數據傳輸。PCB 上平行線(xiàn)的長(cháng)度的任何差異都會(huì )進(jìn)一步增加鏈路的延遲或偏差。

EV12AQ600 亮點(diǎn)亮點(diǎn)

●EV12AQ600 亮點(diǎn)

●高達 6.4 Gsps

●高達 6.5 GHz 帶寬

●集成的交叉點(diǎn)開(kāi)關(guān)

在接收端去除偏差(參考圖 2)和重新對齊數據幀以考慮產(chǎn)生的到達時(shí)間差,需要在 LD 輸出緩沖中實(shí)現靈活的數據緩沖。去除偏差可使接收端的線(xiàn)路正確地對齊。很快我們就會(huì )看到,這是通過(guò)一個(gè)時(shí)間計數器實(shí)現的—— 它訓練系統并建立延遲限制。一旦得出了這個(gè)限制值,則可標記一個(gè)“釋放數據”事件。

EV12AQ600 同步時(shí)鐘

●fCLK & fSSO

●fCLKMAX = 6.4 GHZ (fserial = 2 x fCLK)

●fSSO = fCLK/32

避免亞穩態(tài)

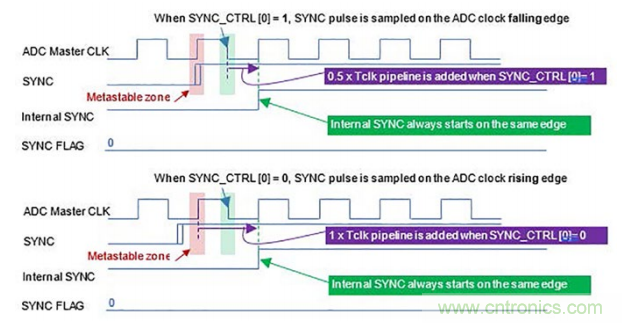

需要強調的一點(diǎn)是,必須保證系統產(chǎn)生的同步信號SYNC 在亞穩態(tài)(MZ)之外采樣。此外,采樣應該始終發(fā)生在相同的ADC 主時(shí)鐘(fCLK)邊緣,以確保整個(gè)多通道采樣系統的確定性延遲。

物理信號偏差

在傳統的 PCB 上,6GHz 的采樣系統在 50 歐姆微帶線(xiàn)(即銅線(xiàn))上通常會(huì )產(chǎn)生6.5ps/mm的傳播延遲。

因此,數據線(xiàn)之間的任何長(cháng)度變化都會(huì )引入額外的傳輸延遲。LD 去偏差緩沖區的大小也應考慮到這個(gè)因素。

P, V, T 的影響

過(guò)程(如半導體制程)、電壓和溫度隨時(shí)間的差異會(huì )影響電子系統的工作點(diǎn)。這也是為什么器件需經(jīng)歷完全的測試、驗證以得出性能參數 —— 即建立 PVT 邊界條件。任何旨在提供確定性延遲的系統都必須足夠健壯,以避免 P、V 或 T 的變化影響確定性。這需要一些控制的機制以允許初始系統校準,以及一個(gè)監控性能隨時(shí)間變化的二階方法。我們稍后將繼續討論這一話(huà)題。

考慮到以上的所有因素,如果同步脈沖和接收輸出緩沖區“有效數據”之間的延遲是固定不變的,則系統的延遲是確定性的(圖 2:釋放數據)。此外,如果經(jīng)歷了多次上電和復位循環(huán)后,延遲的行為可以重現,則這一事件是健壯的。

使用同步標志流程解決 ADC 的亞穩態(tài)

為了避免亞穩態(tài),需引入相對于主時(shí)鐘的門(mén)事件延遲,如圖3 所示。這種方法本質(zhì)上是一種重新計時(shí)的方法。同步 EV12AQ600 的四個(gè)核心需要精確的時(shí)鐘以實(shí)現核心的精確交織。這是 ADC 時(shí)鐘管理單元(CMU)的工作, CMU 還通過(guò) SYNC_CTRL 寄存器(0x000C)實(shí)現亞穩態(tài)緩解功能。在初始化時(shí),ADC 通過(guò)置位SYNC_FLAG 位(0x000D=1)標記出亞穩態(tài)。一旦被置位,SYNC_CTRL寄存器允許用戶(hù)編程ADC 采樣邊緣(圖3)。要避免亞穩態(tài),只需檢查 SYNC_FLAG 是否被重新置位。如果一切正常,則 SYNC_FLAG 保持為低(在 EV12AQ600 的手冊中有SYNC_FLAG 的工作流程)。

圖 2 在 LD 中去除 ADC 輸出數據的偏差

圖 3 同步脈沖延遲避開(kāi)亞穩態(tài)區

同步鏈:一種實(shí)現多通道確定性的簡(jiǎn)單方法

EV12AQ600 的 CMU 提供了解決內部亞穩態(tài)的控制方法。值得注意的是,EV12AQ600 通過(guò)其同步輸出信號(SYNCO)促進(jìn)了同步鏈的實(shí)現。這個(gè)輸出信號可以通過(guò)菊花鏈連接到擴展系統中的其他 ADC 上,可始終保持確定性和相位相干采樣。這對于相位信息至關(guān)重要的系統(如波束形成應用中的合成孔徑雷達(SAR))來(lái)說(shuō)是一個(gè)巨大的優(yōu)勢。雖然這一方法在多通道系統中擴展了確定性采樣,但它只影響模擬前端。它無(wú)法保證發(fā)送到LD 的輸出數據是確定性的。因此,在數字域,我們需要進(jìn)一步的解決方案。

確保數字后端的確定性

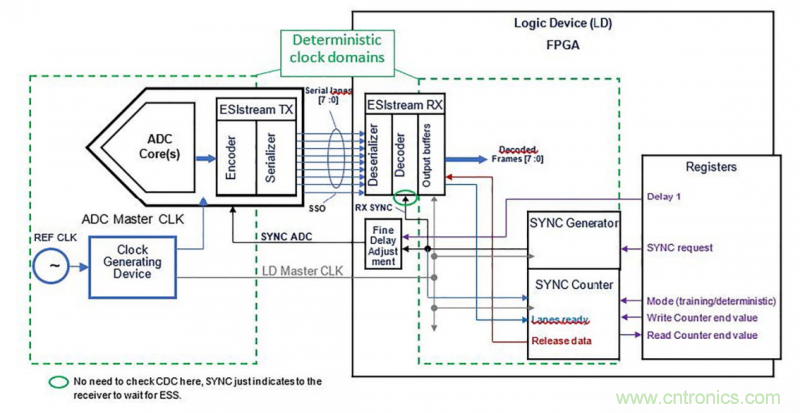

前面的圖 2 顯示了不同的 ESS 的到達時(shí)間有所不同。消除這些線(xiàn)路偏差的一個(gè)低開(kāi)銷(xiāo)的方法是創(chuàng )建一個(gè)延遲計數器——這在LD 中很容易實(shí)現(如圖4)。

計數器累加從 ADC 初始同步脈沖開(kāi)始的時(shí)鐘周期數和LD 接收的最慢的 ESS。在這種情況下,“釋放數據”事件標志著(zhù)接收數據反串行化的完成。通過(guò)訓練系統,同步延遲量化了最慢的 ESIstream 線(xiàn)路的鏈路延遲,包括鏈路層和物理銅線(xiàn)互聯(lián)的影響。

計數器延遲考慮到所有接收緩沖區數據的后續對齊。顯然,在大型分布式系統中,每個(gè)轉換器的數據鏈路延遲不同,需要在初始訓練階段建立。幸運的是,在ESIstream 系統中,同步鏈可輔助加強確定性采樣。同步事件可調整 data ready 信號,并針對最慢的線(xiàn)路進(jìn)行延遲并留有適當的余量,擴展了分布式系統的確定性延遲。

圖 4 同步計數器環(huán)路延遲“data lanes ready”信號,直到最慢的線(xiàn)路準備好

管理 PVT 對確定性的影響

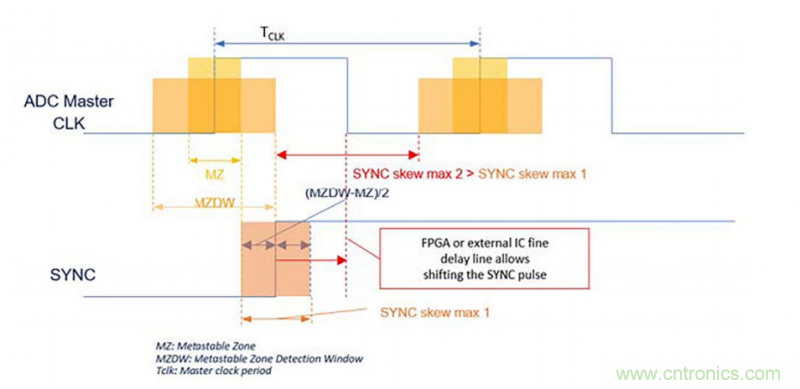

隨著(zhù)采樣頻率的增加,特別是當 EV12AQ600 接近6.4GHz 的上限時(shí),溫度變化引入的時(shí)鐘信號偏差會(huì )導致系統偏離確定性操作,這一點(diǎn)需要加以防范。

Teledyne e2v 提出了以下兩種對策:

• 對系統的溫度變化進(jìn)行參數化描述,以確定其正常工作極限

• 開(kāi)發(fā)一個(gè)動(dòng)態(tài)的微調算法以設置同步脈沖邊緣的位置顯然,后一種方法更復雜,但可在整個(gè)生命周期提供更大的靈活性,也增加了開(kāi)發(fā)的成本。

圖 5 最具挑戰性的系統環(huán)境可能需要精確的延遲方法

熱特性

這里的目標是建議一個(gè)安全的中溫工作點(diǎn),以確保確定性,然后在工作范圍內調整溫度,并監控 ADC 的亞穩態(tài)區(MZ)的 SYNC_FLAG。通過(guò)生成的 MZ 映射,可以確定特定溫度下,對于最佳工作余量的最佳 SYNC_EDGE值(0:上升沿,1: 下降沿)。將這些信息保存在本地查找表里,系統就能夠調整合適的 SYNC_EDGE 應對溫度的變化。

詳細的 MZ 映射有助于避免亞穩態(tài)。這種方法的一個(gè)局限性與老化引入的變化有關(guān)。很難參數化整個(gè)生命周期的性能,也難以得出和時(shí)間相關(guān)的 MZ 映射。在這種情況下,另一種方法可能會(huì )有所幫助。

溫控算法

這是一種動(dòng)態(tài)調整同步脈沖相位偏移(相對于主時(shí)鐘)的算法,可作為 LD 中的一個(gè)額外的時(shí)間延遲模塊來(lái)實(shí)現 —— 例如Xilinx FPGA 中的ODELAY 模塊。 如前所述,首先建立一個(gè)中溫確定性工作點(diǎn)。

然后,使用SYNC_FLAG 流程,在整個(gè)相位范圍內(0 到 360 度)調整同步信號相對主時(shí)鐘的相位,并監視每片 ADC 的SYNC_FLAG 置位事件。這個(gè)過(guò)程建立了同步相位余量的范圍。有了這些信息,確定性操作可通過(guò)以下方式維持:

●設置同步脈沖的最大相位余量

●或動(dòng)態(tài)調整相位以避免亞穩態(tài)

采用任何一種策略都需要仔細的系統級考慮。在高時(shí)鐘頻率下,相位余量受到很大的限制,如圖5 所示。根據權衡和布線(xiàn)的考慮,可能需要引入精細的同步相位調整控制,該控制由每片ADC 外部的時(shí)間延遲IC 提供。

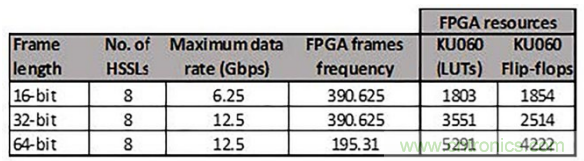

表 1 幀長(cháng)度的選擇決定邏輯資源和數據速率

有一個(gè)因素決定了整體延遲——數據幀長(cháng)度的選擇。這影響邏輯器件的設計。表 1 量化了選擇 1 個(gè)、2 個(gè) 或3 個(gè)字的幀長(cháng)度的影響。

現代的 FPGA 可以解碼高達 400-500MHz 的線(xiàn)路數據速率。然而,實(shí)際應用中還需從經(jīng)濟的角度考慮。某些應用或許只需要較慢的幀速率。這可以用較長(cháng)的幀實(shí)現(表1)。

但是,這種選擇會(huì )影響所需數字資源的復雜度,并隱式地增加總的絕對延遲(圖6)。

圖 6 用單位間隔 (UI) 表示的總系統延遲

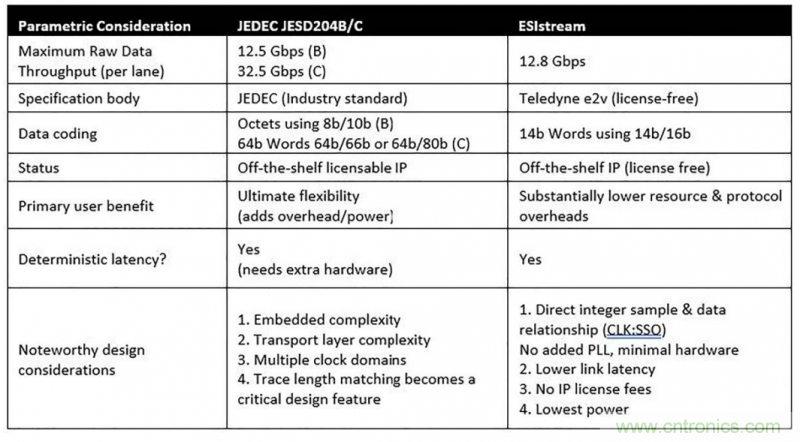

ESISTREAM與JESD204B/C的簡(jiǎn)介

雖然 JESD204B/C 可實(shí)現可重構性,但毫無(wú)疑問(wèn)的是,信號處理行業(yè)對其隱含的復雜性十分警惕。一個(gè)供應商的技術(shù)文檔寫(xiě)著(zhù)“JESD204 生存指南”。這個(gè)問(wèn)題來(lái)源于多時(shí)鐘域和復雜的傳輸層。這兩種方法的高級特性總結如下(表2)。

ESIstream 消除了 JESD204 傳輸層編碼的復雜性,除此之外還有一個(gè)優(yōu)點(diǎn),即它是一個(gè)簡(jiǎn)單的協(xié)議,規范文檔只有 12 頁(yè)。此外,如下的幾個(gè)原因使應用ESIstream 更加簡(jiǎn)單:

• 消除本地多幀時(shí)鐘(LMFC),簡(jiǎn)化了幀結構,幫助調試

• 無(wú)需考慮 PCB 上同步信號布線(xiàn)等長(cháng),因為它在每片轉換器里在SYNCO 輸出端重新計時(shí)到主時(shí)鐘

• 消除外部 SYSREF 信號,因此 ESIstream 通常無(wú)需額外的硬件來(lái)實(shí)現確定性

• 確定性延遲來(lái)源于一次訓練流程。一旦延遲參數被確定,對于給定的設計,這些參數是固定的。因此ESIstream 非常容易投入生產(chǎn)。

表 2 JESD204B/C 和 ESIstream 的特點(diǎn)總結

結論

管理系統設計以確保確定性延遲,這一點(diǎn)在很多高級應用中是至關(guān)重要的。絕對延遲很少是關(guān)鍵性能的決定因素,而固定(有限)的延遲才是重中之重。在超高速系統中,實(shí)現這一目標的難度越來(lái)越大,因為時(shí)間的余量越來(lái)越少。幸運的是,專(zhuān)業(yè)的元器件供應商做了很多努力來(lái)解決這些令人頭疼的問(wèn)題。

以EV12AQ600為例,有如下幾項技術(shù):

●從架構的角度,最簡(jiǎn)單的方法是亞穩態(tài)標志(SYNC_FLAG),它與同步邊沿控制配合,允許調整同步信號的相位,以避免出現不允許的狀態(tài)。

●這個(gè)重新計時(shí)的同步信號可通過(guò)菊花鏈連接到一系列ADC 上,確保整個(gè)擴展系統的相干采樣相位。

●最后,將主時(shí)鐘和同步延遲計數器/發(fā)生器邏輯模塊結合,提供一個(gè)消除 LD 上數據線(xiàn)到達時(shí)間偏差的簡(jiǎn)單的方法。

我們認為無(wú)需許可證的 ESIstream 因其簡(jiǎn)化的數據鏈路層在復雜系統中具有明顯的優(yōu)勢。JESD204B/C (sub-classes 1 和 2)也提供了保證確定性的機制,但據報道,使用這種協(xié)議實(shí)現健壯的鏈接操作非常困難。它的許多技術(shù)挑戰來(lái)源于傳輸層的復雜性,而這種復雜性與它支持的操作的多樣性有關(guān)。

關(guān)于更多的低開(kāi)銷(xiāo) ESIstream 的方案,請訪(fǎng)問(wèn)在線(xiàn)資源中心 ESIstream.com。無(wú)論選擇哪個(gè)方案,確定性延遲都是一個(gè)可實(shí)現的系統設計目標。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請電話(huà)或者郵箱聯(lián)系小編進(jìn)行侵刪。