【導讀】雖然產(chǎn)品可靠性一直以來(lái)都是半導體行業(yè)的一個(gè)重要因素,但隨著(zhù)交通運輸、醫療設備和通信等領(lǐng)域越來(lái)越多地使用電子設備,對于能夠在設計的產(chǎn)品壽命期內按預期工作的集成 電路 (IC) 的需求已呈現出指數級增長(cháng)趨勢。

雖然產(chǎn)品可靠性一直以來(lái)都是半導體行業(yè)的一個(gè)重要因素,但隨著(zhù)交通運輸、醫療設備和 通信等領(lǐng)域越來(lái)越多地使用電子設備,對于能夠在設計的產(chǎn)品壽命期內按預期工作的集成 電路 (IC) 的需求已呈現出指數級增長(cháng)趨勢。然而,盡管對于精準的可靠性驗證的需求已顯 著(zhù)增長(cháng),但使用現有的驗證技術(shù)確保 IC 可靠性一直是 IC 設計公司面臨的重大挑戰之一。技 術(shù)節點(diǎn)尺寸的縮減加上不同類(lèi)型的設計應用的快速增長(cháng),讓該問(wèn)題變得更加復雜,增加了 需要的可靠性檢查數量及其復雜性。所有這些因素都在有力地推動(dòng)對于準確的自動(dòng)化芯片 可靠性驗證方法的需求。如今,Calibre® PERC™ 可靠性平臺 [1] 等全新的電子設計自動(dòng)化 (EDA) 工具應運而生,為設計人員提供了強大的功能來(lái)實(shí)施可靠性檢查,讓他們能夠利用 拓撲、電壓傳播 [2] 和邏輯驅動(dòng)的版圖 (LDL) 功能快速、準確地驗證各種可靠性問(wèn)題。

許多晶圓代工廠(chǎng)現在提供可靠性規則集來(lái)驗證 IC 設計選定的可靠性,其中最常見(jiàn)的是評估靜 電放電 (ESD) 保護和閂鎖效應 (LUP) 事件 [3]。臺積電 (TSMC) 是全球最大的晶圓代工廠(chǎng)之一, 該公司基于 Calibre PERC 可靠性平臺提供完整的 ESD/LUP 規則檢查覆蓋 [4]。TSMC ESD/LUP 套件通過(guò)使用拓撲、點(diǎn)對點(diǎn) (P2P) 電阻、電流密度 (CD) 和基于版圖的 LUP 檢查提供可靠性驗 證 [5,6]。也可以從其他晶圓代工廠(chǎng)獲取可靠性規則集,例如 GLOBALFOUNDRIES [7]、 Samsung [8]、UMC [9] 和 TowerJazz [10]。

晶圓代工廠(chǎng)規則集提供了可靠的可靠性基準,在評估總體可靠性時(shí)應始終用作一線(xiàn)參考。 設計人員可利用這些規則集深入了解晶圓代工廠(chǎng)所重視的 Sign-off 標準。但每家設計公司 通常也會(huì )根據其產(chǎn)品的獨特需求和用途提出額外的可靠性要求。當今的產(chǎn)品設計周期很 短,這也鼓勵設計公司根據自身產(chǎn)品的應用開(kāi)發(fā)自定義的檢查作為晶圓代工廠(chǎng)可靠性驗證 流程的補充,以確保徹底驗證可靠性要求。這些自定義的預編碼檢查可提供額外的有針對 性的可靠性覆蓋,以支持取得市場(chǎng)成功。

不止于晶圓代工廠(chǎng)規則集:自定義可靠性檢查

為確保滿(mǎn)足公司的所有可靠性驗證需求,創(chuàng )建自定義檢查是一種有用而且往往很有必要的 手段。但隨著(zhù)不同應用的可靠性檢查數量以及這些檢查的復雜性日益增加,設計人員需要 一種驗證流程,方便其快速、輕松地選擇和配置這類(lèi)預編碼檢查,而無(wú)需在運行期間管理 檢查的復雜性問(wèn)題。

通過(guò)在簡(jiǎn)單易用的流程中包含精心編寫(xiě)的預編碼檢查,設計人員可以運行這些檢查,而無(wú) 需在運行時(shí)進(jìn)行自定義檢查編碼。為確保設計人員能夠根據需要覆蓋不同的可靠性方面, 該流程必須允許他們組合多項檢查,對目標設計、知識產(chǎn)權 (IP) 模塊或全芯片運行驗證, 這一點(diǎn)也很重要。提供允許設計人員輕松配置和運行自定義檢查及檢查組合的流程,有助 于設計公司在進(jìn)行芯片設計和驗證時(shí),滿(mǎn)足當今日益苛刻的產(chǎn)品上市時(shí)間表。

組合多項檢查

不同的 IC 設計具有不同的可靠性要求和關(guān)注點(diǎn),在驗證期間必須使用各種可靠性檢查對其 進(jìn)行評估。通??赏ㄟ^(guò)選擇和利用規則檢查的組合來(lái)滿(mǎn)足多種驗證需求,其中每項檢查集 中處理一個(gè)特定的方面,從而實(shí)現完整的可靠性驗證覆蓋。

作為說(shuō)明,我們來(lái)看兩項設計應用,一項為多電源域設計,另一項為模擬設計。這些應用 描述了應如何運用不同的可靠性檢查,針對不同的設計提供全面的可靠性驗證覆蓋。在實(shí) 際設計流程中,可能還需要額外的檢查才能實(shí)現所需的全面、嚴格的可靠性驗證。

多電源域應用

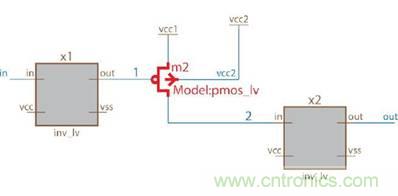

具有多個(gè)電源域的設計存在電氣過(guò)應力 (EOS) 的風(fēng)險。當電參數超過(guò)設計參數時(shí)便會(huì )發(fā)生 EOS。EOS 事件可能造成廣泛的后果,導致不同程度的性能下降,甚至是 IC 永久失效的災 難性損壞 [2]。圖 1 顯示了一種器件級 EOS

條件,其中的一個(gè) PMOS 晶體管的管腳被 連接到不同的電源域。在此示例中,如果 vcc2 被連接到 3.3v,并且柵極切換電壓為 1.8v (vcc1 = 1.8v),則此組合將會(huì )在 m2 柵極 產(chǎn)生氧化應力。這種特殊版圖構成一種微 妙的設計錯誤,會(huì )隨著(zhù)時(shí)間的推移導致失效,而不會(huì )導致立即失效。

圖 1:器件級 EOS 風(fēng)險。

復雜的片上系統 (SoC) 設計具有更多的模擬和數字電路,需要不同的電壓來(lái)支持芯片上的 各個(gè)電源域。具有多個(gè)電源域的設計包含須從一個(gè)電源域跨越到另一個(gè)電源域的信號網(wǎng) 絡(luò ),而這些跨越點(diǎn)經(jīng)常成為故障點(diǎn)或損傷點(diǎn)。因此需要采用保護方案來(lái)控制這些跨域接口處的電壓。設計人員必須插入一個(gè)電平轉換器模 塊,完成從一個(gè)電源/電壓域到另一個(gè)電源/電 壓域的轉換(圖 2)。如果某個(gè)信號網(wǎng)絡(luò )從低壓域 轉移到高壓域而未使用低電平到高電平轉換器, 則該信號網(wǎng)絡(luò )將無(wú)法驅動(dòng)高壓域電路工作。如果 某個(gè)信號網(wǎng)絡(luò )從高壓域轉移到低壓域而未使用高

圖 2:在兩個(gè)不同電源域的信號網(wǎng)絡(luò )之間連接的電平轉 換器電路。

電平到低電平轉換器,則該信號將會(huì )過(guò)驅低壓域 電路,長(cháng)期下去器件將會(huì )受損。因此,缺失電平轉換器會(huì )帶來(lái)可靠性風(fēng)險。設計人員不僅必須驗證各個(gè)域接口部署了適當的電平轉換器, 還要確認連接正確。

驗證這些類(lèi)型的設計需要運行 EOS 檢查來(lái)檢測連接到不同電壓的器件,還需要運行電平轉 換器檢查來(lái)檢測電平轉換器是否存在并且已正確安裝。沒(méi)有這兩項檢查,可靠性驗證便不 完整。

模擬設計性能和老化

模擬電路通常對版圖設計技術(shù)、工作條件和工藝變化的改變非常敏感。在常見(jiàn)的電流鏡等 模擬電路中,器件之間的比率對于實(shí)現正確的設計性能至關(guān)重要。模擬設計的挑戰之一是 實(shí)現并保持準確的比率。此外,模擬設計也很容易受制造工藝中的變化的影響,這可能表 現為制造電路中的意外后果。所有這些版圖挑戰往往會(huì )對電路的可靠性和穩健性產(chǎn)生負面 影響,導致難以設計出在預期的產(chǎn)品壽命期內可靠工作的電路。

需要使用版圖約束,最大限度減小應具備相似行為的器件組(例如差分 對或電流鏡)中存在的這類(lèi)變化 [11]。例如,器件之間的對稱(chēng)檢查可確 保器件全部具有相對水平/垂直軸或中心的對稱(chēng)形狀。對于一系列器 件,檢查器件形狀之間的匹配以及所有器件之間是否具有相同的間距, 可以確保陣列的均勻性。圖 3 顯示了一幅對稱(chēng)不匹配的快照。

圖 3:相對垂直軸的對稱(chēng) 不匹配。

模擬設計的另一個(gè)重要版圖方面是阱區鄰近效應 (WPE)。阱區鄰近是指 器件與其所在阱區的邊緣之間的距離。為使器件對稱(chēng)地老化,阱區中的 所有器件都必須與阱區邊緣具有相同的間距。器件與阱區邊緣之間的距 離即使存在細小的差異,也會(huì )導致器件出現老化差異,從而導致性能下 降,最終縮短產(chǎn)品壽命 [12]。圖 4 顯示了一種 WPE 情形,其中的器件 A、B 和 C 與阱區邊緣具有不同的間隔距離。

為了充分驗證模擬版圖的可靠性,設計人 員通常必須進(jìn)行多項檢查,包括版圖對稱(chēng) 性、器件匹配、WPE、器件之間的間距一 致性,等等。

CALIBRE PERC 組合式檢查流程

通過(guò)使用 Calibre PERC 組合式檢查框 架,設計人員可以快速、輕松地將多 項可靠性檢查組合到一次運行中,進(jìn) 行設計的可靠性驗證(圖 5)。利用 該框架可以輕松地選擇和配置預編碼 檢查,最大限度地提高易用性和減少 運行時(shí)設置。

圖 4:WPE 導致器件老化差異,從而造成長(cháng)期的性 能下降。

圖 5:Calibre PERC 組合式檢查流程。

組合式檢查流程的輸入是一個(gè)用戶(hù)配置文件,設計人員可根據設計需要在其中選擇檢查項 并配置每項檢查的參數。此輸入約束文件由封裝管理器處理,它會(huì )訪(fǎng)問(wèn)檢查數據庫并創(chuàng )建 一個(gè)規則文件,其中包含了所有選定的檢查以及將在指定的設計上運行的正確配置參數。

可靠性覆蓋和可供設計使用的特定檢查的性質(zhì),取決于所參考的特定檢查數據庫中包含的 檢查。參考的庫可能包含全套可用的可靠性檢查,也可能僅包含專(zhuān)門(mén)針對特定設計要求的 子集。特定檢查庫中可能包含的檢查示例包括:

■ 器件計數(所有類(lèi)型和特定類(lèi)型)

■ 電氣過(guò)應力

■ 電平轉換器檢測

■ 查找設計中的圖形

■ 串擾易感性

■ 熱載流子注入效應 (HCI)

■ 拓撲感知的閂鎖

■ 電壓感知的閂鎖

■ 電壓感知的設計規則檢查 (DRC)

■ IO 環(huán)檢查

■ 靜態(tài)供電分析和識別

■ 熱結點(diǎn)識別

■ 阱區鄰近效應易感性(器件老化)

■ 差分對對稱(chēng)

■ 模擬約束檢查

– 對稱(chēng)性、器件匹配、器件的公共質(zhì)心、間 距檢查、參數匹配、集群、器件對齊、虛 擬器件存在

與 Calibre PERC 可靠性平臺中運行的其他規則集一樣,每次檢查都會(huì )生成并報告結果。雖然 組合式檢查可以更輕松地選擇和組合檢查,但在組合中運行多項檢查也會(huì )改變結果的顯示 方式。圖 6 顯示了使用 Calibre PERC 組合式檢查流程的 EOS、電平轉換器和器件計數檢查結 果,其中 EOS 和電平轉換器檢查報告了錯誤結果,器件計數檢查則報告了信息性結果。設 計人員可以使用 Calibre RVE 結果查看器來(lái)對這些結果(包括錯誤和信息性結果)進(jìn)行調試。

圖 6:Calibre RVE 快照 顯示了使用 C alibr e PERC 組合式檢查流程 時(shí)的 EOS、電平轉換器 和器件計數檢查結果。

總結

隨著(zhù)設計復雜性的增加以及對 IP 到全芯片的各級芯片設計可靠性的高度關(guān)注,針對 IC 設計 中的不同可靠性問(wèn)題提供準確且完整的驗證覆蓋至關(guān)重要。要確保設計在產(chǎn)品的使用壽命 內按預期工作,可能需要進(jìn)行晶圓代工廠(chǎng)和自定義的可靠性檢查。利用 Calibre PERC 組合 式檢查流程,設計人員可以自行或在 CAD 或可靠性團隊的指導下,快速、輕松地選擇、配 置和組合多種預編碼檢查。隨后,組合式檢查管理器只需要極少的設置,便可根據所選檢 查自動(dòng)生成一個(gè)規則文件,并啟動(dòng) Calibre PERC 運行,將選定的檢查應用于版圖。然后生 成任何錯誤結果,以便在版圖查看器中查看并進(jìn)行調試和更正。由于設計人員可以使用 Calibre PERC 組合式檢查流程來(lái)選擇和組合檢查,而不必擔心需要針對任何復雜的設置或 運行時(shí)間進(jìn)行編碼,因此能夠更加輕松、快速和一致地運行可靠性驗證,這有助于縮短設 計周期時(shí)間,同時(shí)保障產(chǎn)品可靠性。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請電話(huà)或者郵箱聯(lián)系小編進(jìn)行侵刪。