【導讀】LLC的優(yōu)勢之一就是能夠在比較寬的負載范圍內實(shí)現原邊MOSFET的零電壓開(kāi)通(ZVS),MOSFET的開(kāi)通損耗理論上就降為零了。

LLC的優(yōu)勢之一就是能夠在比較寬的負載范圍內實(shí)現原邊MOSFET的零電壓開(kāi)通(ZVS),MOSFET的開(kāi)通損耗理論上就降為零了。要保證LLC原邊MOSFET的ZVS,需要滿(mǎn)足以下三個(gè)基本條件:

1)上下開(kāi)關(guān)管50%占空比,1800對稱(chēng)的驅動(dòng)電壓波形;

2)感性諧振腔并有足夠的感性電流;

3)要有足夠的死區時(shí)間維持ZVS。

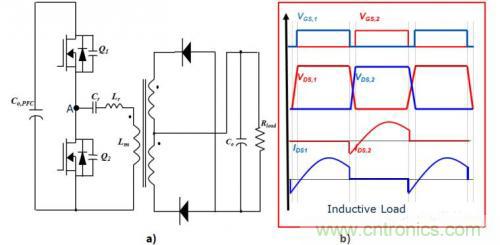

圖a)是典型的LLC串聯(lián)諧振電路。圖b)是感性負載下MOSFET的工作波形。由于感性負載下,電流相位上會(huì )超前電壓,因此保證了MOSFET運行的ZVS。要保證MOSFET運行在感性區,諧振電感上的諧振電流必須足夠大,以確保MOSFET源漏間等效的寄生電容上存儲的電荷可以在死區時(shí)間內被完全釋放干凈。

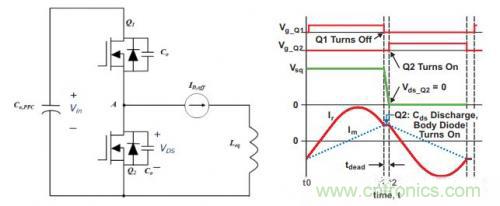

當原邊的MOSFET都處于關(guān)斷狀態(tài)時(shí),串聯(lián)諧振電路中的諧振電流會(huì )對開(kāi)關(guān)管MOSFET的等效輸出電容進(jìn)行充放電。MOSFET都關(guān)斷時(shí)的等效電路如下圖所示:

通過(guò)對上圖的分析,可以得出需要滿(mǎn)足ZVS的兩個(gè)必要條件,如下:

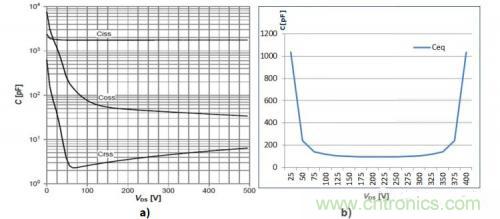

公式看上去雖然簡(jiǎn)單,然而一個(gè)關(guān)于MOSFET等效輸出電容Ceq的實(shí)際情況,就是MOSFET的等效寄生電容是源漏極電壓Vds的函數,之前的文章對于MOSFET的等效寄生電容進(jìn)行過(guò)詳細的理論和實(shí)際介紹。,也就是說(shuō),等效電容值的大小會(huì )隨著(zhù)Vds的變化而變化。如下圖所示,以Infineon的IPP60R190P6為例:

LLC串聯(lián)諧振電路MOSFET的Vds放電過(guò)程分為四個(gè)階段,如下圖所示, (I) 380V-300V; (II) 300V-200V; (III) 200V-100V; (IV)100V-0V。

從圖中可以看出,(I)和(IV)兩部分占據了Vds放電時(shí)間的將近2/3,此時(shí)諧振腔的電感電流基本不變。這兩部分之所以占據了Vds放電的大部分時(shí)間,主要原因在于當Vds下降到接近于0的時(shí)候,MOFET源漏間的寄生電容Coss會(huì )指數的增加。因此要完全釋放掉這一部分的電荷,需要更長(cháng)的LLC諧振周期和釋放時(shí)間。

因此選擇合適的MOSFET(足夠小的等效寄生電容),對于ZVS的實(shí)現至關(guān)重要,尤其是當Vds接近于0的時(shí)候,等效輸出電容要足夠小,這樣還可以進(jìn)一步降低死區時(shí)間并提高LLC的工作效率。

下圖進(jìn)一步說(shuō)明如何選擇合適的ZVS方案。

圖(a):理想的ZVS波形;

圖(b):Vds還沒(méi)下降到0,Vgs已經(jīng)出現。此種情況下,LLC串聯(lián)諧振就會(huì )發(fā)生硬開(kāi)關(guān)。應對之策需要減少變壓器的勵磁電流,或者適當增加死區時(shí)間(如果IC選定,死區時(shí)間一般就固定了);

圖(c):實(shí)現了ZVS,但是諧振腔的電流不足以維持MOSFET體內二極管的持續導通。

圖(d)死區時(shí)間過(guò)于長(cháng)了,會(huì )降低整個(gè)LLC的工作效率。

總之,MOSFET的等效輸出電容對于LLC原邊MOSFET ZVS的實(shí)現是至關(guān)重要的。如果MOSFET已經(jīng)選定,諧振腔需要仔細計算、調試和設定,并選取合適的死區時(shí)間,來(lái)覆蓋所有負載的應用范圍。實(shí)際應用中對于穩態(tài)運行的硬開(kāi)關(guān)都可以通過(guò)設計進(jìn)行修正從而達到穩定運行的設計目的。然而開(kāi)機過(guò)程中的硬開(kāi)關(guān)(軟啟高頻到低頻過(guò)程中),尤其是開(kāi)機過(guò)程中的頭幾個(gè)開(kāi)關(guān)周期,對于有些設計和方案,硬開(kāi)關(guān)是避免不了的。