【導讀】設計簡(jiǎn)單的DCDC電路時(shí),初步計算后就可以根據電感直流電阻(DCR)、電容額定紋波電流和ESR這些都是首先關(guān)注的參數開(kāi)始選型。同樣的,在RF LNA電路中,首先關(guān)心的是RF choke的Q值,疊層磁珠的Q值過(guò)低不宜使用已是共識。但是感容元件的自諧振頻率(Self-Resonant Frequency)這個(gè)"一說(shuō)就會(huì )"的參數卻很容易被新手忽視。在MHz的DCDC和RF LNA電路中,被動(dòng)元件自諧振頻率是需要得到適當關(guān)注的。

設計簡(jiǎn)單的DCDC電路時(shí),初步計算后就可以根據電感直流電阻(DCR)、電容額定紋波電流和ESR這些都是首先關(guān)注的參數開(kāi)始選型。同樣的,在RF LNA電路中,首先關(guān)心的是RF choke的Q值,疊層磁珠的Q值過(guò)低不宜使用已是共識。但是感容元件的自諧振頻率(Self-Resonant Frequency)這個(gè)"一說(shuō)就會(huì )"的參數卻很容易被新手忽視。在MHz的DCDC和RF LNA電路中,被動(dòng)元件自諧振頻率是需要得到適當關(guān)注的。

C0G/NP0類(lèi)的低損耗電容和高Q值RF繞線(xiàn)電感datasheet中一般都會(huì )主動(dòng)標出自諧振頻率的具體值和測試方法。簡(jiǎn)單地說(shuō),電容在低于自諧振頻率的區間內才有作為容性元件的利用價(jià)值,電感在自諧振頻率內才有作為電感的利用價(jià)值。

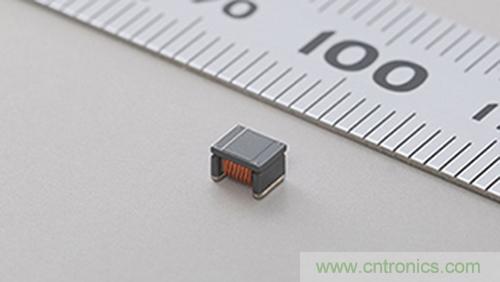

圖1 murata LQW18AS系列spec中的SRF信息

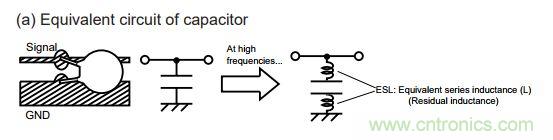

RLC電路中,當系統阻尼R提供的衰減不足時(shí),容抗和感抗相互抵消,能量在LC間來(lái)回傳遞,這就是"諧振"。直插電容的引線(xiàn)、MLCC內部高密度金屬電極和焊接端子都能提供少量的寄生電感(Parasitic Inductance),這是分立電容元件"自"諧振的根本原因。

圖2 電容引線(xiàn)帶來(lái)的寄生電感

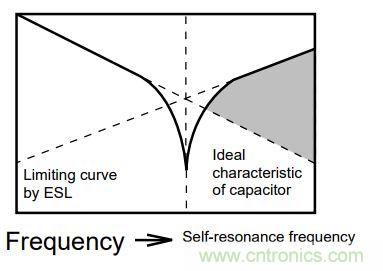

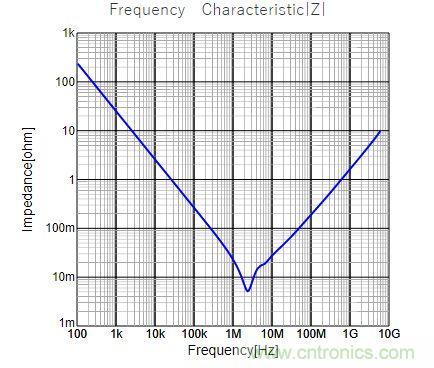

MLCC有經(jīng)典的V型阻抗-頻率曲線(xiàn)。隨著(zhù)頻率升高,寄生電感的影響開(kāi)始凸顯,阻抗先變小再變大,這是MLCC的固有特性。曲線(xiàn)中的最低點(diǎn)就是MLCC的自諧振頻率。

圖3 自諧振頻率在曲線(xiàn)中的位置

一般來(lái)說(shuō),直插件的引線(xiàn)較長(cháng),其寄生電感比SMD大;電解電容內部有大量卷繞結構的鋁箔,寄生電感比其它工藝的電容大。1206尺寸的MLCC內部電極面積和焊接端子截面明顯比0805大,所以尺寸越大的MLCC,自諧振頻率就越低。

圖4 自諧振頻率與尺寸的關(guān)系

事實(shí)上,不同廠(chǎng)家的大尺寸高容MLCC的自諧振頻率大都分布在1-3MHz范圍內,這也剛好也是目前嵌入式系統中追求small solution size DCDC芯片方案的開(kāi)關(guān)頻率范圍。設計MHz DCDC電路時(shí),把電容自諧振頻率加進(jìn)checklist,核算高頻下電容有效容值是否足夠。高效的filter bank對于降低嵌入式系統中板載DCDC的BOM cost、提高系統的功率密度和PCB元件密度都是有好處的。

圖5 三星SEM CL31A106KPHNNNE

圖6 murata GRM188R61A106KAAL

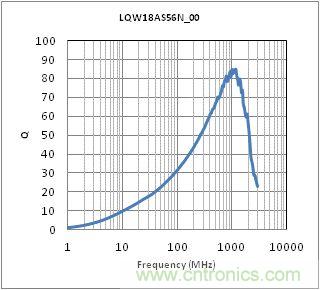

LNA電路直流偏置通路上的RF choke為不同放大器間提供了有效的隔離,避免振蕩——前提是你的電感沒(méi)有超自諧振頻率工作。Q值最高點(diǎn)為自諧振頻率點(diǎn),隨著(zhù)頻率上升,繞線(xiàn)間的寄生電容開(kāi)始搗鬼,Q值快速下降,這會(huì )降低電路的工作效率。SMD的RF繞線(xiàn)電感有不少廠(chǎng)家能生產(chǎn),按需選型即可。

圖7 murata LQW18AS56NJ00

RF電路的信號鏈內經(jīng)常需要一些小電容隔直,電容串聯(lián)在信號通路中,寄生電感和容值的數量級一般不會(huì )對信號質(zhì)量產(chǎn)生明顯影響,但必須要確認電容的耐壓是否滿(mǎn)足信號功率的要求,同時(shí)盡可能選擇S21性能優(yōu)秀的型號,降低插損。

推薦閱讀: