【導讀】泛林集團計算產(chǎn)品部副總裁David Fried接受了行業(yè)媒體Semiconductor Engineering (SE)的采訪(fǎng),探討并分享他對于芯片縮放、晶體管、新型架構和封裝等話(huà)題的看法。

泛林集團計算產(chǎn)品部副總裁David Fried接受了行業(yè)媒體Semiconductor Engineering (SE)的采訪(fǎng),探討并分享他對于芯片縮放、晶體管、新型架構和封裝等話(huà)題的看法。以下內容節選自采訪(fǎng)原文。

Q1:數十年來(lái),集成電路微縮一直是芯片制造行業(yè)推進(jìn)設計進(jìn)步的手段。但是,與之相關(guān)的成本一直在攀升,而且就每個(gè)節點(diǎn)而言,縮小尺寸能體現的優(yōu)勢也在減少。請問(wèn)您怎么看待摩爾定律?我們是否需要2nm甚至更先進(jìn)的制程?是否需要更多的算力?

Dr. Fried:算力全面提升10倍也不嫌多。因為所有的一切都需要算力,包括每個(gè)用戶(hù)交互點(diǎn)、存儲點(diǎn)和每一次計算的節點(diǎn),更高的算力總是有用的,在算力這個(gè)方面的需求沒(méi)有止境。目前的遠程辦公和長(cháng)時(shí)間居家更是進(jìn)一步推動(dòng)了算力需求。

Q2:另外,綜合功率、性能、面積、成本和時(shí)間等來(lái)看,目前整個(gè)行業(yè)似乎在晶體管縮放方面遇到了一些挑戰,具體問(wèn)題包括功耗墻、RC延遲和面積縮放等。您在這個(gè)方面遇到了哪些挑戰?

Dr. Fried:PPAY(即功率、性能、面積和良率)或PPAC(即功率、性能、面積和成本,如果我們想特指成本)一直是所有產(chǎn)品開(kāi)發(fā)避不開(kāi)的要素。我們始終在努力跨越與之相關(guān)的障礙,也一直被PPAC或PPAY制約。我們的目標是推動(dòng)涵蓋所有要素的整體發(fā)展,但有時(shí)在某個(gè)方面的突破可能更明顯一些。但是我們的挑戰來(lái)自于不同的組合,因為整個(gè)系統性能得到提升才是最重要的?;仡櫚l(fā)展的歷史,有時(shí)候只需調整芯片時(shí)鐘頻率就能實(shí)現系統級性能的巨大進(jìn)步,但也有時(shí)是需要通過(guò)電源管理技術(shù)來(lái)做到這一點(diǎn)。無(wú)論如何,我們所面對的最關(guān)鍵要素還是功率、性能、面積以及良率或成本,也就是說(shuō)必須至少在其中一個(gè)領(lǐng)域取得進(jìn)步才能推動(dòng)整體系統性能的提升,而這句話(huà)里的“領(lǐng)域”是在不斷變化的。

在我看來(lái),基線(xiàn)晶體管縮放一直是系統整體性能發(fā)展的一大重要推動(dòng)力,這里的升級可以是任何形式的,包括逐步提升性能、功率表現或晶體管均勻縮放與增強的一致性等?,F在來(lái)看,晶體管縮放顯然還是非常必要的,這體現在很多方面。舉例來(lái)說(shuō),即使不是性能本身的提升,只要縮放能提升密度就值得去努力,因為這樣我們能增加同等面積的核心性能。有些人可能并不在乎晶體管本身的性能提升。但是,如果能通過(guò)晶體管縮放比如將GPU的核心性能增加10%,僅這一點(diǎn)就能讓系統性能向前跨一大步,因為很多原先需要轉到外部處理的數據交互如今在核心內部就可以完成了,這樣處理速度會(huì )有大幅提升。也就是說(shuō),僅僅通過(guò)縮放提升單片集成,也可以實(shí)現巨大的系統級提升。但我們依然要面對此前的制約因素,也一直在各個(gè)方面做出努力。無(wú)論如何,最終的目標始終沒(méi)有變,那就是實(shí)現系統級的性能提升。因此,我們基于PPAC或PPAY采取的一些辦法整體上沒(méi)有太大變化,不存在變革的“拐點(diǎn)”?,F在,我們依然試圖在某些方面取得突破并由此提升系統級的性能。只要市場(chǎng)需求依然存在,我們就能提供更高的算力和存儲。

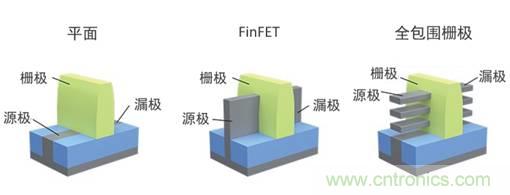

Q3:從2011年開(kāi)始,全行業(yè)開(kāi)始從平面晶體管轉向新一代的FinFET。如今芯片制造商依然在發(fā)展先進(jìn)節點(diǎn)的FinFET晶體管,包括3nm的FinFET以及3nm/2nm的全包圍柵極納米片式晶體管。請問(wèn)您如何看待這種情況?

Dr. Fried:從平面晶體管向FinFET過(guò)渡主要是柵極長(cháng)度縮小的局限性引起的轉變。為更好地控制器件的靜電,整個(gè)行業(yè)都轉向了雙柵極架構,這就涉及到幾納米的柵極縮放,并進(jìn)一步創(chuàng )造了新的晶體管縮放維度。我們可以提升高度,讓同等封裝面積有更大的有效寬度,這樣可以讓整個(gè)過(guò)渡更平穩。全包圍柵極好處在于完全控制器件的靜電,這將帶來(lái)額外幾個(gè)納米的柵極縮放。而正是這幾個(gè)納米的差異開(kāi)啟了新的縮放維度。如果將來(lái)我們可以實(shí)現互補式FET——例如彼此堆疊的nFET和pFET——這將給我們額外的邏輯縮放優(yōu)勢。

我們從獲得靜電控制優(yōu)勢開(kāi)始,以實(shí)現柵極長(cháng)度縮放,并由此創(chuàng )造了全新的縮放維度。盡管如此,從FinFET過(guò)渡到全包圍柵極(納米線(xiàn)或納米片)可能沒(méi)有之前這么順利,因為新的架構需要我們在結構之下執行工藝,這是一個(gè)非常大的改變,且具有挑戰性。在FinFET時(shí)代,我們需要在側壁上更好地執行半導體工藝,但我們仍然可以看到整個(gè)過(guò)程。在全包圍柵極納米片/納米線(xiàn)結構中,處理過(guò)程中所涉及的架構將是看不到的,這樣進(jìn)行測定的難度就會(huì )大幅提升。因此,向全包圍柵極過(guò)渡更具有挑戰性。

Q4:您如何看待先進(jìn)封裝、單片集成等替代架構?

Dr. Fried:我們應該歡迎在系統層面的任何創(chuàng )新,包括晶體管縮放、芯片架構改進(jìn)和3D集成化封裝,綜合所有這些進(jìn)步才能滿(mǎn)足最高的系統性能要求?,F在的市場(chǎng)對系統的需求非常多樣化。曾經(jīng)的市場(chǎng)沒(méi)有這么分化,當時(shí)一切都是以CPU為重?;乜催^(guò)去,我們曾經(jīng)的系統級性能改進(jìn)方案很像是瑞士軍刀,也就是說(shuō)所有的方法,無(wú)論對應的是晶體管、互連、封裝還是集成,都是為一個(gè)更大的整體方案服務(wù)。

如今,市場(chǎng)需求已經(jīng)出現多樣化,每個(gè)系統都有自己獨特的需求。如果沿著(zhù)這些多樣化的路徑發(fā)展,我們可能需要在晶體管、封裝和互連等每個(gè)領(lǐng)域做出不同的方案,也就是說(shuō)要以不同的方式優(yōu)化每個(gè)系統。例如,由于不同系統有不同的要求和需求,一個(gè)3D集成方案的內存、I/O和計算單元配置可能完全不同于另一個(gè)方案的配置。這里面要抉擇的東西非常多,一旦芯片架構發(fā)生變化,相關(guān)的技術(shù)、封裝和互連方法也要隨之改變。我很期待能看到這樣多樣化的系統性能要求究竟能給這個(gè)行業(yè)帶來(lái)怎樣的變化。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請電話(huà)或者郵箱聯(lián)系小編進(jìn)行侵刪。