【導讀】模擬開(kāi)關(guān),是利用JFET或MOS的特性實(shí)現控制信號通路的開(kāi)關(guān),主要用來(lái)完成信號鏈路連接或斷開(kāi)的切換功能。由于它具有功耗低、速度快、無(wú)機械觸點(diǎn)、體積小和使用壽命長(cháng)等特點(diǎn),在各種自動(dòng)控制系統和電子數碼產(chǎn)品中得到了廣泛應用。

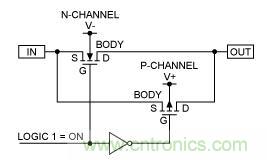

傳統CMOS工藝模擬開(kāi)關(guān)的結構如圖1所示。將NMOS與PMOS并聯(lián),可使信號在兩個(gè)方向上同等順暢地通過(guò)。門(mén)極用于控制開(kāi)關(guān)的導通和截止,NMOS在Vgs為正的時(shí)候導通,在Vgs為負的時(shí)侯截止,PMOS則反之。由于PMOS和NMOS的不同特性,導致他們組成的開(kāi)關(guān)具有如下圖所示的特性。NMOS和PMOS之間承載信號電流的多少由輸入與輸出電壓比決定。由于開(kāi)關(guān)對電流流向不存在選擇問(wèn)題,因而也沒(méi)有輸入端與輸出端之分。兩個(gè)MOSFET由內部反相與同相邏輯控制下導通或斷開(kāi)。CMOS開(kāi)關(guān)的好處是軌到軌的動(dòng)態(tài)范圍,雙向操作,在輸入電壓變化時(shí),導通電阻保持不變。

圖1 典型模擬開(kāi)關(guān)內部結構圖

● 靜態(tài)參數(導通電阻,漏電流,邏輯控制觸發(fā)電平):

①導通電阻RON,不同通道導通電阻的差異RON,導通電阻的平坦度RFLAT(ON)

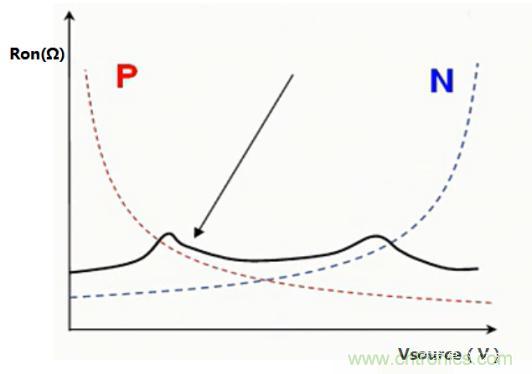

導通電阻會(huì )導致信號有損失,尤其是當開(kāi)關(guān)串聯(lián)的負載為低阻抗時(shí)損失更大。應用中應根據實(shí)際情況選擇導通電阻合適的開(kāi)關(guān)。特別需要注意,導通電阻的阻值與電源供電電壓有直接關(guān)系,通常電源電壓越大,導通電阻就越小。

圖2 CMOS型模擬開(kāi)關(guān)導通電阻特性曲線(xiàn)

NMOS管在信號比較低時(shí)的導通電阻較小,而PMOS管則在輸入信號較高時(shí)的導通電阻較小,兩個(gè)電阻并聯(lián)后,則在整個(gè)信號的有效范圍內都比較低。

②漏電流Leakage Current :

一個(gè)理想狀態(tài)的開(kāi)關(guān)要求導通狀態(tài)下的電阻為零,斷開(kāi)狀態(tài)下導通電阻趨于無(wú)限大,漏電流為零;而實(shí)際上開(kāi)關(guān)斷開(kāi)時(shí)為高阻狀態(tài),漏電流不為零,常規的CMOS漏電流約1nA左右。開(kāi)關(guān)斷開(kāi)時(shí),漏電流會(huì )流入負載,從而引起額外的誤差。如果信號源內阻很高,傳輸信號為直流量,就特別需要考慮模擬開(kāi)關(guān)的漏電流,一般希望漏電流越小越好。

需要注意,如果通過(guò)模擬開(kāi)關(guān)前端電路的阻抗大則漏電流的影響不容忽略,如果前端電路阻抗較小,則導通電阻的影響就會(huì )更大些。

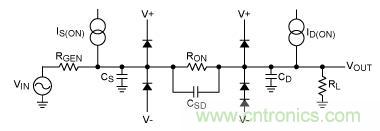

圖3 開(kāi)關(guān)導通狀態(tài)下的等效電路

③邏輯控制觸發(fā)電平VIH,VIL:

VIH:可以被模擬開(kāi)關(guān)識別成邏輯高電平的最小電平值

VIL:可以被模擬開(kāi)關(guān)識別成邏輯低電平的最大電壓值。

l 動(dòng)態(tài)參數(導通斷開(kāi)時(shí)間,傳輸延遲,電荷注入,管腳電容,最大數據速率,隔離度等)

①Ton/Toff:

開(kāi)關(guān)接收到數字控制管腳的導通或斷開(kāi)信號后,輸出真正反映輸入信號導通或斷開(kāi)所需要的時(shí)間。

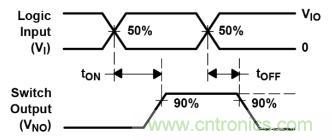

圖5 Turn on&Turn off 時(shí)間

②T-break-before-make:

這個(gè)指標大部分針對單刀多擲的模擬開(kāi)關(guān)而言的,比如對于一個(gè)1:2的模擬開(kāi)關(guān)(SPDT),它的定義是從斷開(kāi)一個(gè)開(kāi)關(guān)到打開(kāi)另一個(gè)開(kāi)關(guān)的時(shí)間。

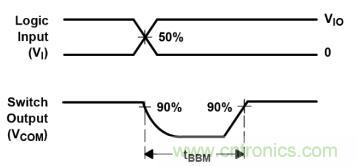

圖6 Break-Before-Make時(shí)間

③T-make-before-break:

與上面的參數類(lèi)似,從打開(kāi)開(kāi)關(guān)到斷開(kāi)另外一個(gè)開(kāi)關(guān)的時(shí)間。

④切換時(shí)間:T transition time:

從一個(gè)輸入通道切換到另一個(gè)輸入通道后,輸出需要的切換時(shí)間。

⑤T enable/disable time:

輸入通道在使能和禁止時(shí),所需要的的時(shí)間。

⑥Propagation delay:

信號出現在輸入通道后,出現在輸出通道的時(shí)間差。

⑦電荷注入:

用于衡量模擬開(kāi)關(guān)在進(jìn)行開(kāi)和斷操作時(shí)由于電荷的放電,導致出現在開(kāi)關(guān)輸出的毛刺電壓。原理是開(kāi)關(guān)導通時(shí),對電容進(jìn)行充電斷開(kāi)時(shí),儲存的電荷進(jìn)行放電。對源端的放電不會(huì )引入誤差,而對負載端的放電則會(huì )引入誤差。顯而易見(jiàn),電荷注入會(huì )帶來(lái)增益誤差和直流失調誤差。

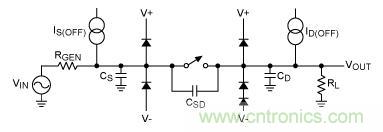

⑧管腳寄生電容Cs(on),Cd(on),Cs(off),Cd(off),C in

Cs(on) 導通時(shí)輸入電容

Cd(on) 導通時(shí)輸出電容;

Cs(off) 斷開(kāi)時(shí)的輸入電容;

Cd(off) 斷開(kāi)時(shí)的輸出電容;

C in 數字控制引腳上的寄生電容。

⑨-3dB帶寬-3dB Bandwidth:

開(kāi)關(guān)導通時(shí),增益衰減3dB的時(shí)候,可導通信號的頻率被定義為帶寬。

⑩隔離度Off Isolation:

當開(kāi)關(guān)斷開(kāi)時(shí),理想狀態(tài)下,輸出不應出現輸入信號,實(shí)際上在輸出會(huì )有與輸入信號頻率一樣的信號,這是由于輸入輸出間的寄生電容引起的。隔離度參數越大越好,表示輸出端耦合過(guò)去的信號越小。

串擾Crosstalk:

對于2:1的復用器,當其中通道1導通時(shí),通道2上會(huì )耦合出通道1的信號,Crosstalk用于衡量耦合信號的大小,參數值越大,表示耦合過(guò)去的信號幅值越小。

總諧波失真Total Harmonic Distort:

一些音頻的信號處理對THD要求嚴格,THD定義為,信號功率與諧波及噪聲的dB比值。測試時(shí)給開(kāi)關(guān)輸入一個(gè)正弦波,開(kāi)關(guān)的輸出會(huì )包含基波以及各次諧波,要注意的是導通電阻的平坦度也會(huì )影響THD的指標。

模擬開(kāi)關(guān)應用場(chǎng)景

潤石科技深耕細分領(lǐng)域,為不同的應用場(chǎng)景量身打造了多個(gè)系列的模擬開(kāi)關(guān):

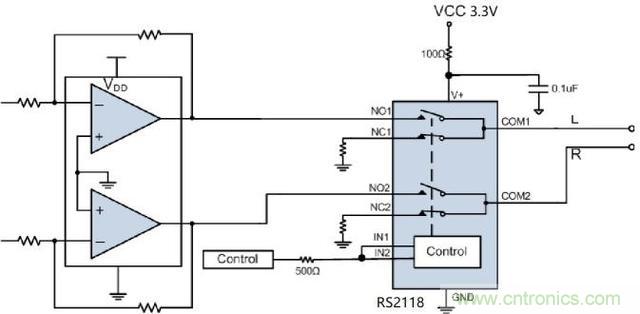

①音頻類(lèi)應用:RS2117/RS2118非常適合用于降噪耳機,音箱,KVM、矩陣以及調音臺等產(chǎn)品中。在音頻系統中,對模擬開(kāi)關(guān)的要求是可以過(guò)交流信號,并且需要消除瞬時(shí)放電脈沖通過(guò)揚聲器時(shí)引起的POP音。這些瞬時(shí)脈沖通常由電源的通、斷引起。下圖是用RS2118設計的一種消除POP音的電路:

圖7 RS2118 POP音消除電路

②通訊口擴展

USB接口復用:帶寬550MHz模擬開(kāi)關(guān)RS2227/RS2228

SPI接口復用,I2S信號切換:帶寬300MHz模擬開(kāi)關(guān)RS2299

UART、I2C接口擴展:RS2105/RS2058等

③多路信號分時(shí)采樣

當電路中需要采集的信號量比較多的時(shí)候,ADC或者IO口不夠用的時(shí)候可以使用模擬開(kāi)關(guān)來(lái)做端口的擴展。在滿(mǎn)足帶寬和電源要求的情況下,RS2251/RS2252/RS2254多路復用器可以輕松應對這樣的需求。

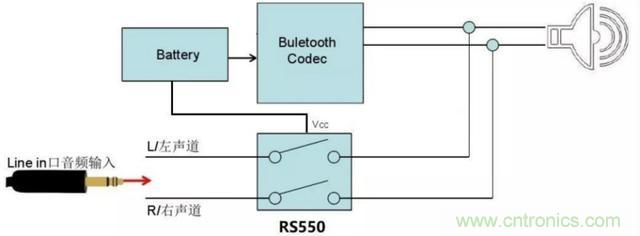

④耗盡型模擬開(kāi)關(guān)RS550

當降噪耳機的電池電量耗盡時(shí),或者需要控制外部輸入的音源直接接入到音源時(shí),可以直接使用耗盡型的模擬開(kāi)關(guān)RS550,不供電下處于閉合導通狀態(tài)。

圖8 RS550在降噪耳機上的應用示意

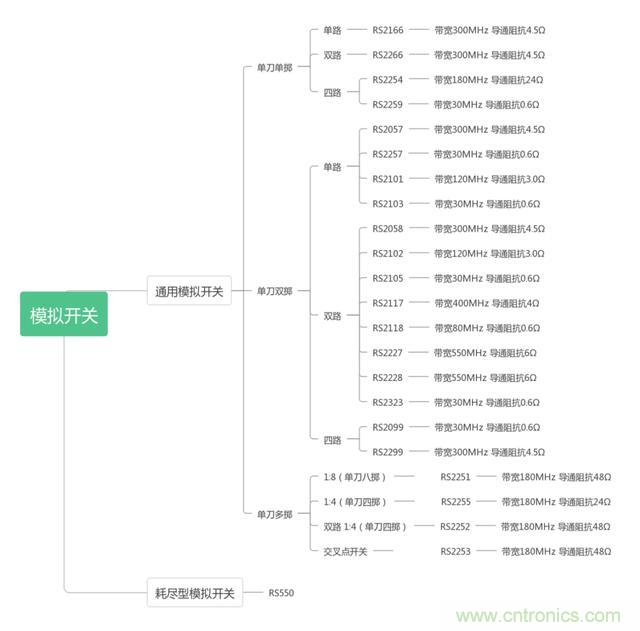

附:潤石科技模擬開(kāi)關(guān)選型樹(shù)狀圖

圖9 潤石模擬開(kāi)關(guān)選型樹(shù)狀圖

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請聯(lián)系小編進(jìn)行處理。

推薦閱讀: