【導讀】精密測量已延伸到需要越來(lái)越高電源效率的應用領(lǐng)域。物聯(lián)網(wǎng)的到來(lái)使這一點(diǎn)尤為明顯,因為物聯(lián)網(wǎng)更加需要具有精密測量能力的無(wú)線(xiàn)傳感器節點(diǎn),電池供電的可穿戴健身/醫療設備,以及使用隔離電源供電、4 mA到20 mA環(huán)路供電或電池供電現場(chǎng)儀表的工業(yè)信號鏈。在這些場(chǎng)景中,電源效率越高,意味著(zhù)電池使用時(shí)間越長(cháng),維護越少,電源設計越簡(jiǎn)單。

通常,精密測量系統將低壓差穩壓器(LDO)作為其電源方案的一部分,利用它來(lái)為精密ADC產(chǎn)生低噪聲電源軌。然而,LDO的功率輸出效率非常低下,大部分功率常常作為熱量損失掉。本文討論為精密逐次逼近型(SAR) ADC實(shí)現更高效率電源解決方案的途徑。實(shí)現方法是在遲滯模式下使用超低功耗開(kāi)關(guān)穩壓器,并分析性能得失——包括通過(guò)某種方式來(lái)智能控制開(kāi)關(guān)穩壓器,使之與SAR轉換同步,從而改善噪聲性能。

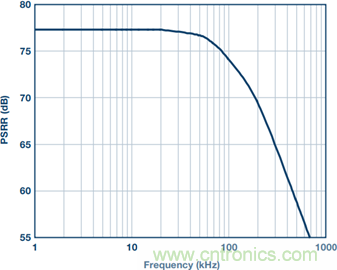

在中高負載電流(數百mA到數A)的測量系統中,固定頻率或脈寬調制(PWM)開(kāi)關(guān)穩壓器可非常有效地(常常大于90%)產(chǎn)生電源軌。然而,效率雖然高,但代價(jià)是會(huì )有開(kāi)關(guān)紋波,其頻率通常是固定的,從數百kHz到數MHz。如圖1所示,典型精密SAR ADC的電源抑制比(PSRR)在低頻至約100 kHz時(shí)是非常好的——超過(guò)此頻率時(shí),PSRR迅速下降。

圖1. SAR ADC模擬電源抑制與頻率的關(guān)系

精密SAR ADC以較低吞吐速率運行時(shí),供應VDD線(xiàn)的典型負載電流在數mA或μA范圍——因此,相比于LDO,使用固定頻率開(kāi)關(guān)穩壓器直接為ADC供電在效率上沒(méi)有優(yōu)勢。

然而,高效率、超低功耗降壓開(kāi)關(guān)穩壓器可在遲滯模式下工作,其靜態(tài)電流非常低。

在遲滯模式下,通過(guò)調節恒定峰值電感電流,穩壓器利用PWM脈沖使輸出電壓略高于標稱(chēng)輸出電壓。當輸出電壓提高到輸出檢測信號超過(guò)遲滯上限時(shí),穩壓器進(jìn)入待機模式。在待機模式下,高端和低端MOSFET及大部分電路都禁用,靜態(tài)電流很低,效率性能很高,如圖2所示。待機模式期間,輸出電容將能量送入負載,輸出電壓降低到低于遲滯比較器下限為止。穩壓器喚醒,產(chǎn)生PWM脈沖,再次對輸出充電。

圖2. PWM(上圖)和遲滯模式(下圖)——效率與負載電流的關(guān)系

在遲滯情況下,開(kāi)關(guān)紋波頻率與負載電流和LC網(wǎng)絡(luò )有關(guān);對于數mA的負載,其在kHz范圍內。在數kHz時(shí),精密ADC的PSRR非常好,能夠很好地抑制/衰減ADC數字輸出端的開(kāi)關(guān)紋波。

以圖3所示電路為例,它使用AD7980ADC;在全吞吐速率(1 MSPS)時(shí),其VDD電流消耗典型值為1.5 mA;若降低吞吐速率,電流消耗 會(huì )按比例線(xiàn)性下降。這可從圖4看出:采用5 V電壓軌供電時(shí), 2.5 V穩壓輸出端的開(kāi)關(guān)頻率紋波為4.5 kHz和50 mV峰峰值。在A(yíng)DC數字輸出端,ADC以PSRR額定值衰減此紋波。在A(yíng)DC FFT輸出中,它表現為幅度−120 dBFS、頻率4.5 kHz的雜散。對于A(yíng)DC的5 V輸入范圍,這相當于

圖3. AD7980和ADP5300應用電路

圖4. ADP5300為AD7980供電時(shí)的遲滯開(kāi)關(guān)紋波(交流耦合),以及1 MSPS吞吐速率時(shí)的ADC FFT輸出中的紋波音

出現在A(yíng)DC輸出端的這種紋波水平對一個(gè)16位轉換器而言是非常低的;5 μV峰峰值對應于16位下的0.07 LSB。這種水平的紋波會(huì )被埋在A(yíng)DC噪底中,需要大量均值操作才能發(fā)現,在很多應用中都不會(huì )看到它。此輸出紋波對應的PSRR為

該要求與圖1所示相似,AD7980在4.5 kHz時(shí)的PSRR約為77 dB。

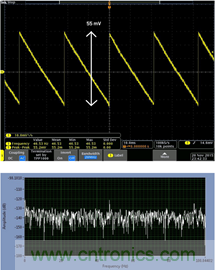

若ADC吞吐速率降低到10 kSPS,則ADC的電流消耗按比例線(xiàn)性下 降到15 μA (約100倍),ADP5300 的開(kāi)關(guān)頻率紋波相應地降低到 46.5 Hz (約100倍),幅度為55 mV峰峰值,如圖5所示。在46 Hz時(shí),該紋波再次在A(yíng)DC FFT輸出中出現,幅度為−120 dB (5 μV峰峰值),因為在該頻率的PSRR相似。有證據表明存在93 Hz的二次諧波,其幅度更低,為−125 dB。

圖5. ADP5300為AD7980供電時(shí)的遲滯開(kāi)關(guān)紋波(交流耦合),以及10 kSPS吞吐速率時(shí)的ADC FFT輸出中的紋波音

圖6對照顯示了ADP5300和LDO在不同ADC吞吐速率時(shí)的效率,兩種情況均采用5 V電壓軌供電,調節2.5 V輸出。同預期一樣,開(kāi)關(guān)穩壓器輸送功率的效率遠勝于LDO,在1 MSPS時(shí)是90%對50%(針對5 V輸入),在較低ADC吞吐速率/較低電流消耗時(shí)保持得也更好,始終高于80%,直至5 kSPS。

圖6. ADP5300和LDO的效率與ADC吞吐速率的關(guān)系

ADC吞吐速率為1 MSPS且使用LDO時(shí),從5 V電壓軌消耗的電流為1.5 mA或7.5 mW。使用ADP5300時(shí),從5 V電壓軌消耗的電流為828 μA或4.1 mW,即ADC電源的功耗減少3.4 mW或45%。

使用ADP5300作為VDD電源以及10 kHz近滿(mǎn)量程輸入信號(−0.5 dB),AD7980在1 MSPS時(shí)的性能如圖7所示。在SNR (91.5 dB)和THD (−103 dB)方面,ADC仍然符合數據手冊規格。然而,ADP5300的4.5 kHz開(kāi)關(guān)紋波會(huì )在輸入信號上進(jìn)行調制,顯示為10 kHz – 4.5 kHz (5.5 kHz)和10 kHz + 4.5 kHz (14.5 kHz)的雜散。這些雜散仍然處于非常低的水平(−116 dBFS),遠小于基波信號的二次諧波引入的THD(其在20 kHz時(shí)為−103.8 dBFS)。在16位水平時(shí),這些偽像只是一個(gè)LSB的很小一部分,因而在許多應用中,考慮到ADP5300穩壓器的省電優(yōu)勢,這是完全可以接受的。

圖7. AD7980使用ADP5300作為VDD電源時(shí)的性能基波信號周?chē)梢钥吹介_(kāi)關(guān)紋波調制引起的邊頻帶(10 kHz ±4.5 KHz)

ADP5300開(kāi)關(guān)穩壓器有一個(gè)STOP (停止)切換特性,它可以完全消 除開(kāi)關(guān)紋波偽像,使其不會(huì )出現在A(yíng)DC FFT輸出中。當STOP處于高電平時(shí),ADP5300的STOP引腳就會(huì )阻止SW引腳切換。在對噪聲敏感的ADC轉換過(guò)程中,可利用該特性防止切換發(fā)生。為實(shí)現這一功能,CNV信號和STOP信號應連在一起(參見(jiàn)圖3),并且對來(lái)自處理器的CNV信號進(jìn)行定時(shí),使其在A(yíng)DC轉換時(shí)保持高電平。對于A(yíng)D7980,此時(shí)間最大值為710 ns,轉換在CNV上升沿啟動(dòng)。結果如圖8所示。這種情況下的紋波頻率更加變化不定,因為只有在特定時(shí)間,SW節點(diǎn)才會(huì )開(kāi)啟和調節。另請注意,從STOP信號變?yōu)榈碗娖降絊W開(kāi)啟的時(shí)間可能為數百ns。圖8中,STOP下降沿后大約850 ns,SW引腳開(kāi)啟。這意味著(zhù),當ADC吞吐速率為1 MSPS時(shí),我們不能使用STOP特性,因為SW引腳將沒(méi)有足夠的時(shí)間來(lái)變?yōu)楦唠娖讲⒄{節,VDD電源將失去調節而崩潰。STOP功能在吞吐速率為500 kSPS或更低時(shí)有效。

圖8. 500 kSPS時(shí)使用STOP功能的ADP5300開(kāi)關(guān)紋波(黃色)、CNV/STOP信號(藍色)及ADP5300的SW引腳(粉紅)

從圖9可以看出,使用STOP信號后,ADC噪底中完全不存在開(kāi)關(guān)紋波雜散。當施加10 kHz的輸入信號時(shí),除一般諧波之外,基波周?chē)鷽](méi)有調制。然而,當SW引腳禁用(STOP為高電平)時(shí),由于SW引腳上的振鈴,使用STOP特性的效率會(huì )下降。對于500 kHz的ADC吞吐速率,ADP5300的效率降至約75%。這仍然顯著(zhù)高于LDO能夠實(shí)現的效率(<50%),并且提供了一個(gè)功耗>

圖9. AD7980使用ADP5300作為VDD電源時(shí)的性能,STOP特性時(shí)序根據轉換周期進(jìn)行調整

ADP5300等開(kāi)關(guān)穩壓器解決方案與LDO解決方案在成本和PCB面積方面具有一定的可比性。BOM主要增加一個(gè)電感,2.2 μH電感可以小到0603封裝,而對于輸入和輸出電容,LDO解決方案同樣需要。因此,在功耗敏感型應用中,它是LDO的有力替代方案,對精度性能并無(wú)明顯影響。

當從5 V電源軌為AD7980等精密ADC供電時(shí),ADP5300等高效率、超低功耗開(kāi)關(guān)穩壓器與LDO相比,可節省45%的功耗。這對物聯(lián)網(wǎng)應用(延長(cháng)無(wú)線(xiàn)傳感器節點(diǎn)或可穿戴設備的電池使用壽命)、功耗敏感型隔離式工業(yè)系統、4 mA至20 mA環(huán)路供電系統有很多好處。

推薦閱讀: