【導讀】在有多個(gè)供電電源的系統中,運算放大器電源必須在施加輸入信號的同時(shí)或之前建立。否則,便可能發(fā)生過(guò)壓和閂鎖狀況。然而,在實(shí)際應用中,這個(gè)要求有時(shí)候可能難以滿(mǎn)足。本文討論運算放大器在不同上電時(shí)序情況下的行為表現(參見(jiàn)表2),分析可能的問(wèn)題及原因,并提出一些建議。

上電時(shí)序問(wèn)題多種多樣

上電時(shí)序問(wèn)題可能出現于多種不同情況。例如,在一個(gè)客戶(hù)應用中,AD8616配置為緩沖器,在電源建立之前輸入為0 V(圖1),負電源先于正電源上電(負電源有而正電源無(wú))。

圖1. AD8616測試電路,施加–3 V V–,V+沒(méi)有連接電源

表1顯示了這種情況下AD8616所有引腳的結果。在正電源管腳V+上的信號建立之前,V+引腳和OUT引腳上的電壓為負值。這可能不會(huì )損害運算放大器,但若這些信號連接到其他尚未完全供電的芯片上的引腳(例如,假設ADC使用同一V+,其電源引腳一般只能承受最小–0.3 V電壓),則這些芯片可能會(huì )受損。如果V+先于V–上電,會(huì )發(fā)生同樣的問(wèn)題。

表2列出了上電時(shí)序的一些可能情況。

表1. 施加–3 V V–而V+沒(méi)有連接電源時(shí)的AD8616引腳電壓

表2. 上電時(shí)序的可能情況IN

運算放大器內部的靜電放電(ESD)二極管

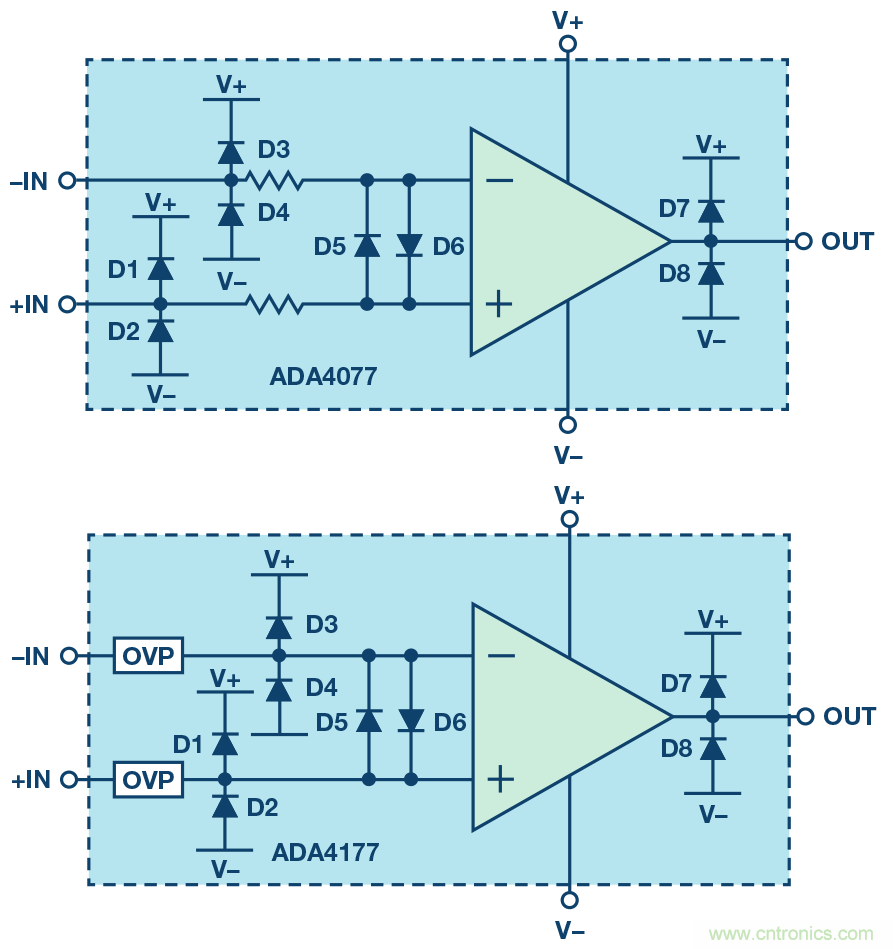

靜電放電可能引起過(guò)壓事件。大部分運算放大器內置ESD二極管 以防止靜電ESD事件。當V+或V–不存在時(shí),ESD二極管是分析放大 器相關(guān)行為的重要工具。圖2為ADA4077/ADA4177的簡(jiǎn)化框圖。表3 顯示了ADA4077-2/ADA4177-2內部ESD二極管和背靠背二極管的典 型壓降。注意,背靠背二極管位于運算放大器的兩個(gè)輸入引腳之間, 用來(lái)箝位放大器允許輸入的最大差分信號。

圖2. ADA4077/ADA4177簡(jiǎn)化框圖

表3. 運算放大器內部二極管

還要注意,當利用DMM測量ADA4077-2的D5/D6時(shí),結果顯示兩個(gè)輸 入引腳之間無(wú)二極管。事實(shí)上,背靠背二極管之前有兩個(gè)串聯(lián)電阻, 用來(lái)將輸入電流限制在±10 mA以下。內部電阻和背靠背二極管將 差分輸入電壓限制在±Vs,以防止基極-發(fā)射極結點(diǎn)擊穿。

A DA4177集成了OVP單元以提高魯棒性。它們位于ESD二極管和 背靠背二極管之前,因此很難用DMM測量這些二極管的管壓降。 ADA4177的輸出ESD二極管的管壓降是可以測量的。

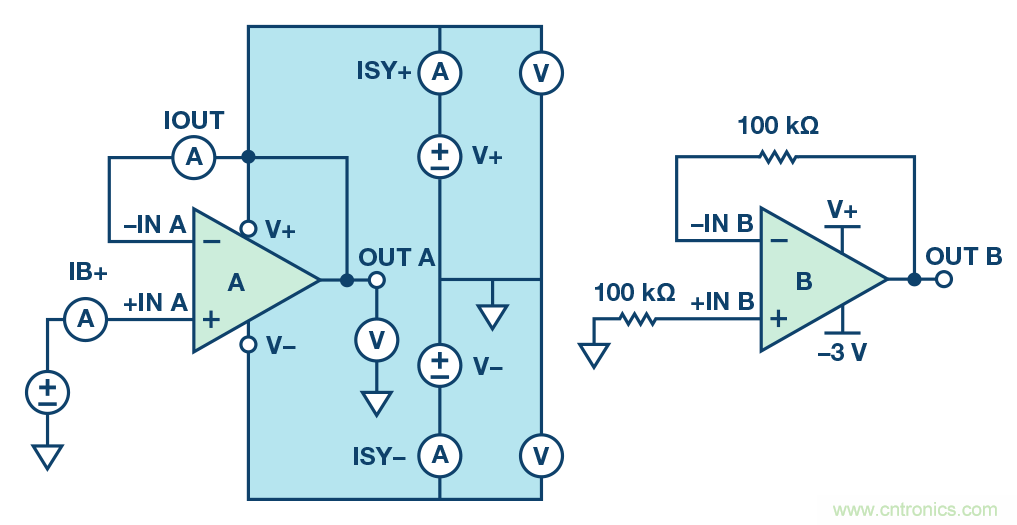

建立評估系統

圖3用于測量運算放大器電路的電流流向等行為。通道A和通道B各 自配置為緩沖器,通道B同相輸入端經(jīng)由100 kΩ電阻連接到GND。讓 V+不供電(V–供電)或V+供電(V–不供電),便可利用安培表和電 壓表測量輸入及電源相關(guān)變量(電壓值和電流值)。通過(guò)分析這些 變量,可以確定電流流動(dòng)的路徑。

圖3. 放大器電流路徑評估系統建立

情形1:輸入懸空

表4顯示了一個(gè)輸入懸空和一個(gè)電源未供電時(shí)的結果。當V–供電而 V+不供電時(shí),V+引腳上有一個(gè)負電壓。當V+供電而V–不供電時(shí),V– 引腳上有一個(gè)正電壓。

測試ADA4077-2和ADA4177-2得到類(lèi)似的結果。輸入引腳和電源引 腳上沒(méi)有觀(guān)測到大電流,輸入懸空的運算放大器在一個(gè)供電軌沒(méi) 有供電時(shí)仍然是安全的。

情形2:輸入接地

表5顯示了輸入接地時(shí)的結果。注意,對于IB+,負值意味著(zhù)電流流 出+IN引腳。對于IOUT,負值意味著(zhù)電流流出–IN引腳。

表4. ADA4077-2/ADA4177-2輸入懸空時(shí)的結果

表5. ADA4077-2/ADA4177-2輸入接地時(shí)的結果

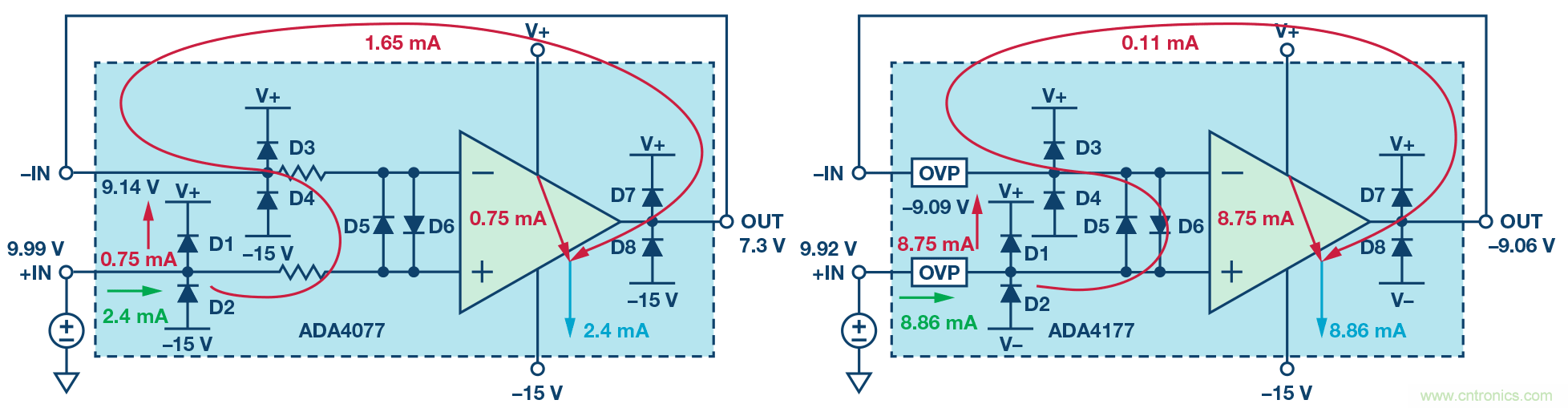

以ADA4077-2 V+未上電的情況為例,ESD二極管將V+箝位于VIN電壓。

1.VIN通過(guò)E S D箝位二極管連接到V+,因此當V I N為0 V時(shí),V+ 為–0.846 V。

2.電流流動(dòng)路徑:如圖4中的紅色路徑所示,0.7 mA電流從GND (+IN)流到V+。1.6 mA電流從GND (+IN)經(jīng)過(guò)內部電阻、D5以及–IN 和OUT之間的反饋路徑,流入輸出端。最后,這兩個(gè)電流(0.7 mA 和1.6 mA)匯合流至–15 V,合并后的電流流回GND (+IN)。

ADA4177-2和ADA4077-2的結果類(lèi)似。注意,ADA4177-2中的D1是通 過(guò)橫向PNP晶體管的發(fā)射極基極實(shí)現的。該晶體管將過(guò)壓電流從V+ 帶走到V–。圖4中的ADA4177電路顯示有9.1 mA電流從V+流回V–,并 與反饋路徑中的0.2 mA電流匯合,產(chǎn)生9.3 mA電流流至–15 V,然后 該電流流回GND。

ADA4077-2或ADA4177-2的輸入引腳和電源引腳均未觀(guān)測到大電流(表 5)。增益為+1且+IN接地時(shí),這些運算放大器可承受任何時(shí)序的PU上電。

情形3:有輸入

在一個(gè)電源未上電的情況下,將一個(gè)正信號或負信號(+10 V或-10 V) 施加于+IN端。表6顯示沒(méi)有大電流,因此當增益為+1且+IN有輸入時(shí), 這些運算放大器可承受任何順序的PU上電。

電流流動(dòng)路徑分析與情形2(0 V輸入)相似,參見(jiàn)圖5。

圖4. V+未上電時(shí)ADA4077/ADA4177電流路徑(輸入接地)

圖5. V+未上電時(shí)ADA4077/ADA4177電流路徑(10 V輸入)

表6

情形4:有輸入且電源/輸出有負載

在實(shí)際應用中,運算放大器電路可能要與其他電路一起工作。例如, 運算放大器的輸出可能會(huì )驅動(dòng)一個(gè)負載,或者運算放大器的電源 會(huì )為其他電路供電。這會(huì )引起問(wèn)題。

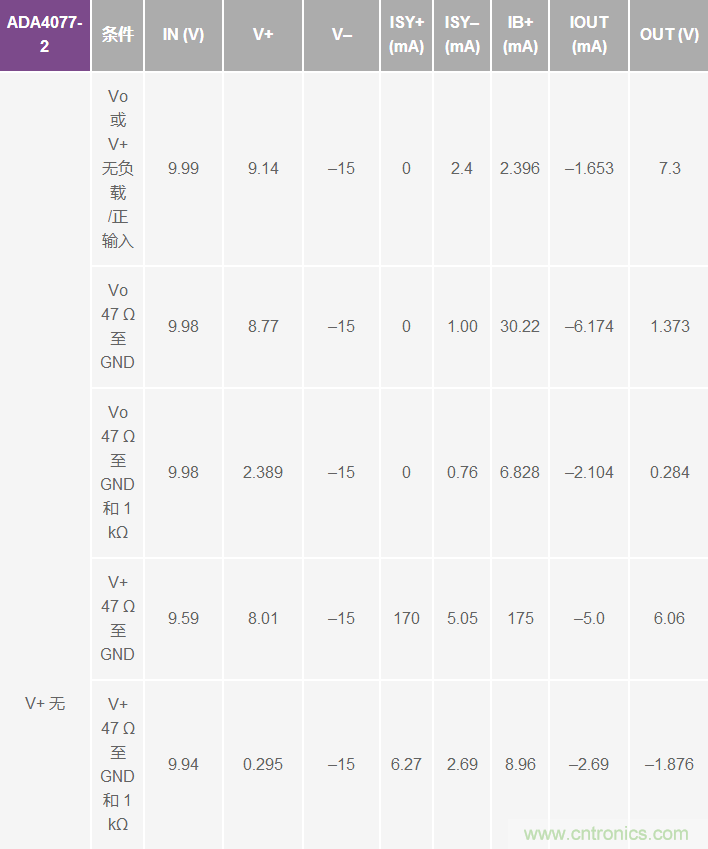

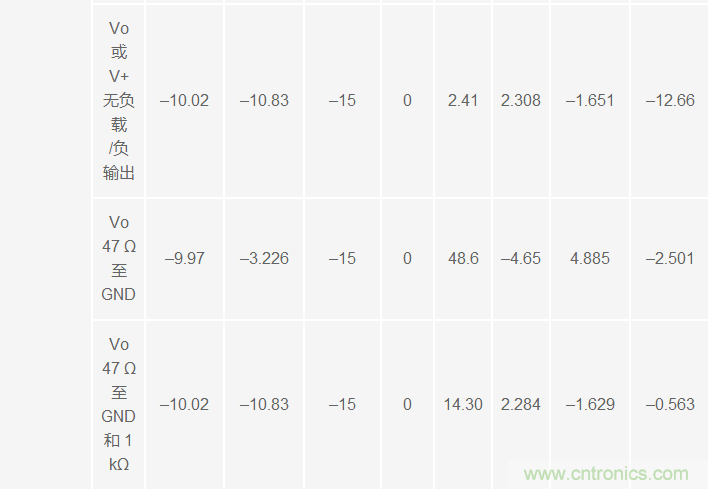

在該測試中,一個(gè)47 Ω電阻連接在輸出與GND之間,或連接在未上 電的電源引腳與GND之間。圖7顯示了ADA4077的測試結果。三種可 能情況會(huì )帶來(lái)風(fēng)險(假定V+未上電):

情況1:當輸入為10 V且OUT負載為47 Ω時(shí),輸出為1.373 V。有23 mA電流從運算放大器的輸出引腳流出(參見(jiàn)圖6),電流路徑為:

1.輸入信號源提供30.2 mA電流

2.24 mA電流流經(jīng)D1至V+,6.2 mA電流流經(jīng)D5和反饋路徑至OUT

3.來(lái)自V+的24 mA電流分為1 mA(至V–)和23 mA(至OUT)

4.29.2 mA電流流經(jīng)47 Ω負載至GND

ADA4077-2允許的輸入電流最大為10mA,所以需要限流。在+IN端 增加一個(gè)1 kΩ電阻,可使輸入電流降至6.8 mA。

情況2:當輸入為10 V且V+負載為47 Ω時(shí),170 mA電流會(huì )流入 ADA4077-2,并從V+引腳流出到47 Ω電源負載。170 mA電流會(huì )燒 毀內部二極管,損壞芯片。在+IN端增加一個(gè)1 kΩ電阻,可使輸入 電流降至8.9 mA。圖7顯示了電流流動(dòng)路徑。

表7.ADA4077的輸出引腳或無(wú)電源的電源引腳上有負載

圖6. V+未上電時(shí)ADA4077的電流路徑(10 V輸入和47 Ω輸出負載)

圖7. V+未上電時(shí)ADA4077的電流路徑(10 V輸入和47 Ω電源負載)

情況3:當輸入為負(-10 V)且OUT負載為47 Ω時(shí)(參見(jiàn)圖8),有48 mA電流流經(jīng)芯片。由此產(chǎn)生的功耗為48 mA × (–2.5 V + 15 V) = 0.6 W。ADA4077-2的θJA為158°C/W,因此結溫比環(huán)境溫度高出 94.8°。若有兩個(gè)通道或負載更重,結溫可能高于150°,致使芯片 受損。

不應在輸入端增加限流電阻,而應在輸出端增加限流電阻。

當V+上電而V–未上電時(shí),會(huì )發(fā)生同樣的現象。通過(guò)增加外部電 阻來(lái)限制電流,電路魯棒性可以變得更好。

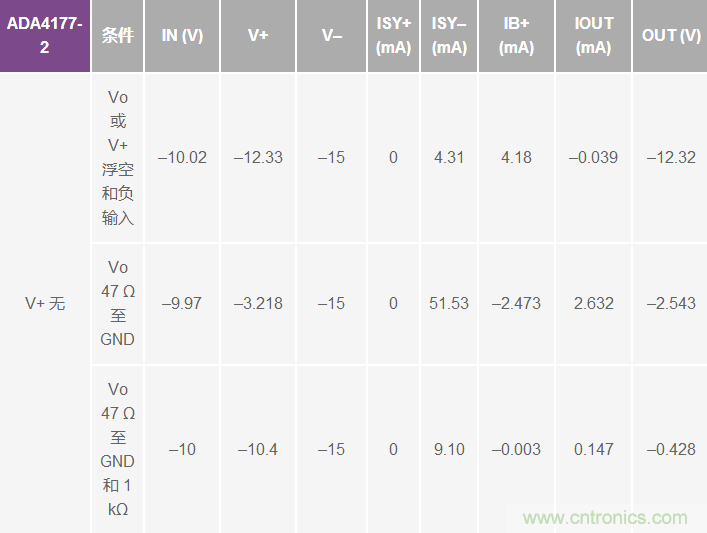

對于A(yíng)DA4177-2,僅情況3適用。當有很大的負輸入,同時(shí)輸出端有 很重的負載,且V+未上電時(shí),有53 mA電流流經(jīng)芯片,功耗可能會(huì ) 增加,結溫隨之提高(參見(jiàn)圖9)。通過(guò)在輸出端增加一個(gè)1 kΩ電阻, 可以避免這種風(fēng)險。

在這兩款運算放大器中,ADA4177-2比ADA4077-2更魯棒。在同時(shí)要 求高精度和魯棒性的應用中,前者是不錯的選擇。

其他運算放大器在不同上電時(shí)序下的表現

在運算放大器內部,二極管、電阻和OVP單元有各種各樣的實(shí)施方式。 有些運算放大器沒(méi)有內部OVP單元,有些沒(méi)有背靠背二極管,有些沒(méi) 有內部限流電阻。如果一個(gè)電源未上電,放大器不同的內部結構會(huì )產(chǎn) 生不同的結果。此外,不同的運算放大器設計也會(huì )產(chǎn)生不同的結果。

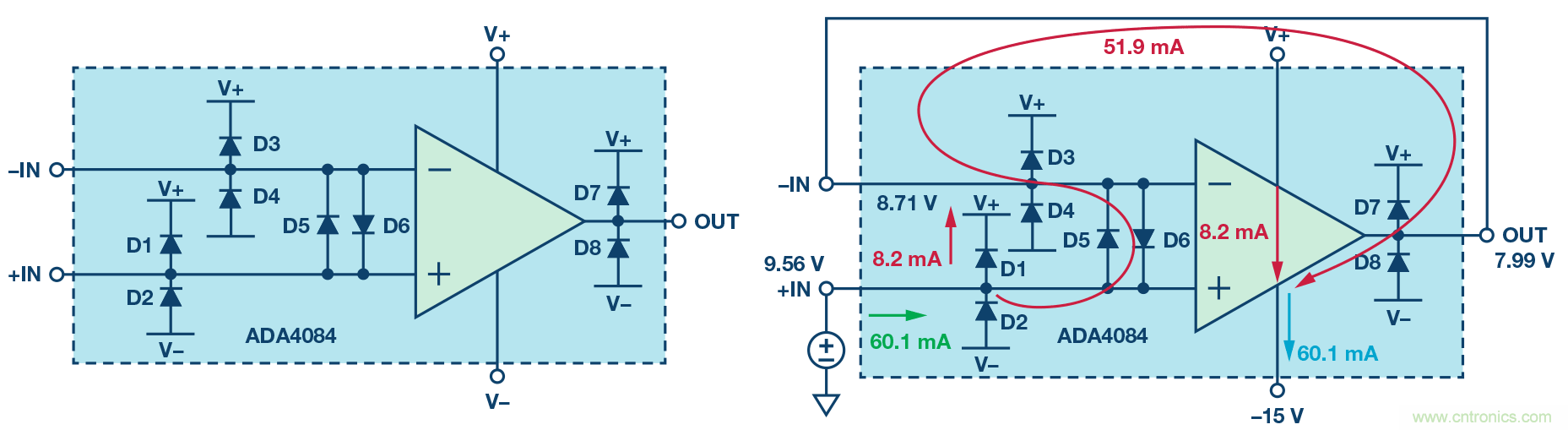

例如,ADA4084-2沒(méi)有內部限流電阻和OVP單元,其ESD二極管連接 到電源和背靠背二極管。表9和圖10顯示了V+未上電且有10 V輸入 時(shí)的結果。ADA4084的電流路徑與ADA4077-2和ADA4177-2相似(上 文中的情形3已討論)。然而,ADA4084沒(méi)有內部電阻或OVP單元來(lái) 限制電流,60 mA電流會(huì )流入芯片,可能引起損害。

圖8. V+未上電時(shí)ADA4077的電流路徑(-10 V輸入和47 Ω輸出負載)

圖9. V+未上電時(shí)ADA4177的電流路徑(-10 V輸入和47 Ω輸出負載)

圖10. V+未上電時(shí)ADA4084的電流路徑(10 V輸入)

表8. ADA4177的輸出引腳或無(wú)電源的電源引腳上有負載

表9

在系統應用中,不同的運算放大器、不同的拓撲結構(如同相放大、 反相放大、差動(dòng)放大等)、不同的負載和外部連接都可能存在。如 果存在有某個(gè)電源未上電的情況,需要對風(fēng)險進(jìn)行評估。本文介紹 了如何搭建評估風(fēng)險的電路(圖2)、如何分析電流路徑以及評估潛 在的風(fēng)險。

總結

為了避免過(guò)壓或閂鎖情況,必須同時(shí)建立運算放大器電源。一般指 南如下:

1.上電時(shí),先接通電源,再在輸入端施加信號

2.關(guān)斷時(shí),先關(guān)閉輸入信號,再關(guān)閉電源

在實(shí)際應用中,可能難以遵守這些指導原則。這可能會(huì )引起問(wèn)題, 尤其是當有輸入信號時(shí),設計人員需要適當評估風(fēng)險。一種有效的 解決方案是限制運算放大器的輸入電流,使它在數據手冊給出的 規格以?xún)?。在無(wú)法同時(shí)上電的應用中,輸入端和輸出端增加限流電 阻會(huì )有幫助。

我們在電源未上電的應用中測試了三款ADI運算放大器(ADA4084-2、 ADA4077-2和ADA4177-2)。集成內部電阻的ADA4077-2表現不錯。集 成OVP電路的ADA4177的魯棒性最好。在某個(gè)電源在某個(gè)時(shí)間段可 能未上電且無(wú)法增加外部限流電阻的應用中,推薦使用ADA4177以 避免精度性能下降。

推薦閱讀: