【導讀】目前,智能家居、工業(yè)自動(dòng)化、自動(dòng)駕駛、醫療保健、智能可穿戴設備等智能連接設備和智能手機對于數據容量需求的不斷增長(cháng),為了滿(mǎn)足這一需求,5G電信標準應運而生。通過(guò)使用“大規模多輸入多輸出”(massing-MIMO)天線(xiàn)陣列,5G讓每個(gè)基站能夠進(jìn)行更多的數據連接。

現有的4G基站,每個(gè)陣列最多使用四個(gè)發(fā)射器和四個(gè)接收器(4x4 MIMO)。與之相比,預計采用大規模MIMO陣列的5G基站,每個(gè)陣列可使用多達64個(gè)發(fā)送器和64個(gè)接收器。加之每個(gè)基站節點(diǎn)有更多的信道,5G網(wǎng)絡(luò )能比4G網(wǎng)絡(luò )的數據傳輸速率高100倍,并且網(wǎng)絡(luò )延遲低至1ms。

這將意味著(zhù)每個(gè)5G基站需要更多的調制解調器,數據轉換器和高速基帶數字處理器,也就不可避免地需要更多的電源供給。預估表明,5G基站可能比現有4G基站多三倍的功率需求,需要硬件設計師找到合適的電源解決方案,為新增的處理器供電,并將所有元器件能被壓縮到和現有4G基站機殼差不多的尺寸中。對比傳統分立式 DC / DC IC和外部電感的解決方案,5G基站的電路板組件密度要求更高,尺寸要求更小,且需要實(shí)現更高的效率和更低的EMI。

基站的輸入電壓通常為48V,該電壓被DC / DC轉換器降壓至24V或12V,然后進(jìn)一步降壓到多個(gè)電源軌,范圍從3.3V至1V以下,這些電源軌為基帶處理器中的ASIC電路供電。

傳統的電源解決方案是使用分立式降壓DC/DC變換器,采用一個(gè)控制IC,使用內置或者外置的功率MOSFET,再加上外部電感和電容等元件,產(chǎn)生所需的電源軌。由于5G基站需要的電源軌眾多,如果使用傳統的解決方案,產(chǎn)生這些電源軌將會(huì )是一個(gè)非常復雜而耗時(shí)的任務(wù)。不僅必須要考慮每個(gè)轉換器的電感尺寸和結構、輸入輸出電容容值、輸入濾波,還要考慮到其他因素,例如工作頻率和時(shí)序等問(wèn)題。

同時(shí),為了減少開(kāi)關(guān)電流引起的傳導和輻射EMI,還需要精心對元件布局和放置濾波器組件。DC / DC轉換器通常會(huì )通過(guò)電流回路中的磁場(chǎng)產(chǎn)生傳導EMI,而電流回路主要形成在輸出功率MOSFET開(kāi)關(guān)節點(diǎn)與地之間以及輸入電容與地之間。MOSFET開(kāi)關(guān)節點(diǎn)與電感連接處也會(huì )產(chǎn)生輻射電場(chǎng)EMI,由于需要不斷在輸入電平與地電平切換,因此dV / dt很高,并且電感本身產(chǎn)生的電磁場(chǎng)也會(huì )產(chǎn)生輻射(見(jiàn)圖1)。

圖 1:DC / DC降壓轉換器的典型EMI噪聲源

如果設計不當,會(huì )造成極其耗時(shí)耗費的設計迭代和重復EMI測試。

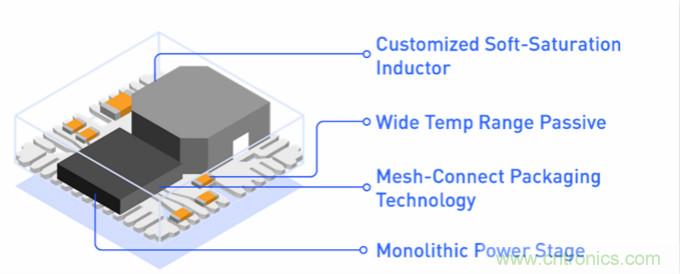

為了簡(jiǎn)化設計并加快產(chǎn)品上市速度,一種替代的解決方案是在每個(gè)電源軌上使用獨立的DC / DC轉換器模塊。隨著(zhù)半導體工藝技術(shù)和封裝結構的進(jìn)步,MPS最新一代的DC / DC模塊可以實(shí)現小尺寸、高功率密度、高效率和良好的EMI性能。同時(shí),新的封裝技術(shù),例如倒裝工藝和“mesh-connect”引線(xiàn)框架技術(shù),可以將IC、電感和無(wú)源器件直接安裝在引線(xiàn)框架上,無(wú)需打線(xiàn)或額外的內部PCB (見(jiàn)圖二)。

圖2:集成模塊DC / DC降壓變換器結構

引線(xiàn)框架結構優(yōu)點(diǎn)明顯,它可以更好地控制EMI,改善散熱,并能減少占板面積。

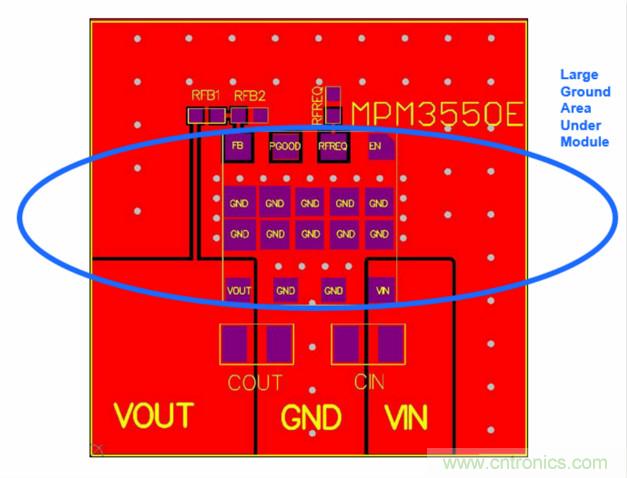

與采用內部PCB基板或打線(xiàn)的結構相比,此種結構可以最大限度地減少走線(xiàn)長(cháng)度,并能直接連至無(wú)源元件,大大降低了寄生電感,減少了EMI。而且表面直接貼裝在目標PCB上的焊盤(pán)柵格陣列(LGA)封裝,和SIP/SIL封裝的變換器相比,其EMI更少,因為SIP/SIL封裝的引腳會(huì )輻射EMI。同時(shí),LGA封裝允許接地層覆蓋模塊下方的大部分區域,有助于閉合渦流環(huán)路而進(jìn)一步降低EMI(見(jiàn)圖3)。 對于有些類(lèi)型的模塊電源,其金屬外殼還可以減少額外的EMI輻射。

圖 3:模塊較大接地層面積有助于降低EMI

T使用銅柱直接將MOSFET裸片的源極和漏極連接到模塊的引線(xiàn)框架上,可以改善從功率MOSFET到目標PCB覆銅的熱傳導,實(shí)現更小的模塊尺寸,而傳統結構中的打線(xiàn)或內部電路板結構則會(huì )阻礙散熱。

MPS 產(chǎn)品MPM3550E采用集成模塊的方法,大大節省了布板空間。該模塊可以在 1V 至 12V 可調輸出電壓范圍內實(shí)現 5A 的最大持續輸出電流,最大輸入電壓高達36V,采用尺寸為12mmx12mmx4.2mm 的LGA封裝。

與帶有外部電感和無(wú)源元件的傳統36V、3.5A分立式DC / DC布局相比,MPM3550E的占板面積可節約30%的空間 (見(jiàn)圖四)。

圖 4: DC / DC降壓模塊尺寸對比傳統分立式DC / DC解決方案尺寸

除了節省空間外,設計人員也無(wú)需再考慮獨立元件的選型或轉換器的布局。這些問(wèn)題已經(jīng)在MPS的模塊設計時(shí)被考慮。MPS的電源模塊集成了軟飽和磁芯的封閉式磁路電感、優(yōu)化的電流環(huán)路和集成輸入濾波,能大大簡(jiǎn)化最終設計,確保滿(mǎn)足輻射和傳導EMI要求。

由兩個(gè)10μF電容和一個(gè)3.3μH電感的組成的LC低通濾波器,足以滿(mǎn)足傳導發(fā)射規范,包括CISPR22 Class B 和CISPR25 Class 5規范 (見(jiàn)圖5)。

圖 5:帶有外部EMI濾波器的模塊性能圖及傳導EMI結果

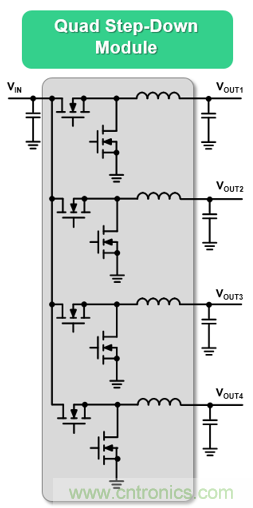

為了進(jìn)一步節省電路板空間,一種可行的辦法是將多個(gè)DC/DC變換器集成到一個(gè)模塊中。這尤其適用于低壓電路,例如ASIC。較低的功率等級允許多個(gè)變換器集成到一個(gè)模塊的同時(shí),仍能實(shí)現可控的功率密度和功耗水平。(見(jiàn)圖六,圖七)。

圖 6:集成4個(gè)DC/DC變換器模塊示例

圖 7:集成4個(gè)DC/DC模塊的小尺寸封裝圖

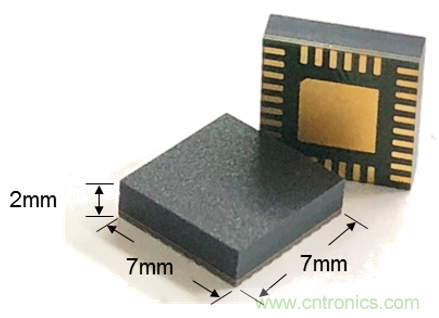

與使用獨立DC/DC電源變換器的解決方案相比,采用多電源軌模塊方案,可以節約高達90%的占板面積。圖8顯示的是MPS 的電源模塊MPM54304,與四個(gè)分立的降壓轉換器占用面積的比較,MPM54304將四個(gè)降壓轉換器包括電感和無(wú)源元件集成在單個(gè)7mmx7mmx2mm模塊中。

圖 8:四個(gè)分立式DC / DC轉換器與MPM54304的占板空間的比較

毋容置疑的是,5G基帶和無(wú)線(xiàn)電板設計對于元件集成度和功率密度的要求更高,同時(shí)還會(huì )受到安裝機柜尺寸和無(wú)線(xiàn)電天線(xiàn)桿負載能力的限制。而使用DC / DC集成模塊可以幫助節省電路板空間,簡(jiǎn)化布局和降低EMI。 綜上所述,MPS的解決方案不但可以降低設計風(fēng)險,還能縮短產(chǎn)品上市時(shí)間。

推薦閱讀: