【導讀】在PCB設計實(shí)際運用中,控制電源噪聲的關(guān)鍵就是降低電源回路的阻抗。本節讓我們來(lái)探討下我們設計中經(jīng)常遇到的麻煩問(wèn)題,這種問(wèn)題往往帶來(lái)的就是大量工作量的修改,我們跨分割是否允許,信號換層是否能夠接受以及如何改善它們?

承前:電源噪聲是由電流回路阻抗和瞬態(tài)電流共同作用引起的。在PCB設計實(shí)際運用中,控制電源噪聲的關(guān)鍵就是降低電源回路的阻抗。所以我們在設計過(guò)程中一定要關(guān)注電源隱藏的回路。

本節:讓我們來(lái)探討下我們設計中經(jīng)常遇到的麻煩問(wèn)題,這種問(wèn)題往往帶來(lái)的就是大量工作量的修改,我們跨分割是否允許,信號換層是否能夠接受以及如何改善它們?

設計到后期階段如果出現了重要信號跨分割,那肯定就要修改優(yōu)化,如果項目密度稍微大點(diǎn),我們就得整上個(gè)以天來(lái)計算的改動(dòng)。在避免發(fā)生這個(gè)的時(shí)候,我們得先來(lái)分析why?同樣的對于信號換層,換到哪層更好也來(lái)分析下。

設計到后期階段如果出現了重要信號跨分割,那肯定就要修改優(yōu)化,如果項目密度稍微大點(diǎn),我們就得整上個(gè)以天來(lái)計算的改動(dòng)。在避免發(fā)生這個(gè)的時(shí)候,我們得先來(lái)分析why?同樣的對于信號換層,換到哪層更好也來(lái)分析下。

跨分割

話(huà)說(shuō)不能腳踏兩只船,那在PCB設計中該如何了?跨分割到底是怎么一回事,與返回路徑有關(guān)嗎?有什么壞處?

a,我們設計時(shí)在參考平面跨了分割(以跨同一平面來(lái)解釋?zhuān)缤暾牡仄矫嬗幸粭l間隙),,這使得返回路徑被迫繞道而行,返回路徑與信號路徑之間的阻抗將會(huì )比之前的加大,從而造成返回路徑上阻抗的不連續。(當到參考平面的環(huán)路面積增大的時(shí)候,阻抗變大)。

b,我們從不同信號返回路徑重疊的情況分析,信號返回路徑上是會(huì )有串擾。由于這個(gè)間隙的存在,許多與之信號路徑平行的其他信號,返回時(shí)阻抗最小的路徑都是在這個(gè)間隙段,使這里成為串擾的集中點(diǎn)。電流的交疊是不會(huì )有串擾的,串擾來(lái)自由于信號路徑與返回路徑包成的面積增加,而形成了一個(gè)近場(chǎng)耦合器類(lèi)似的東西。

c,我們從EMI角度上看,我們知道當回流信號遇到不連續處時(shí),這個(gè)不連續處就會(huì )形成一個(gè)回路,而回路面積和EMI有關(guān),這就造成了一個(gè)本不存在的EMI問(wèn)題,建議改為EMC。

信號換層

信號換層無(wú)法避免,那換層時(shí)回流路徑怎么破?

a,信號換層時(shí),最好不要改變參考層。在這種情況下,返回路徑無(wú)需換層,即信號的換層對其返回路徑?jīng)]有影響。

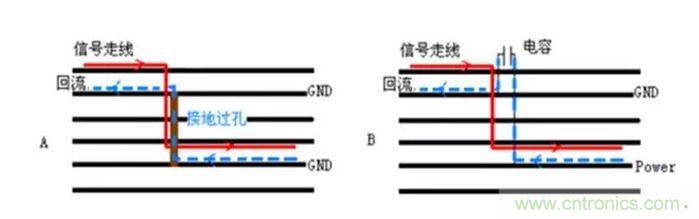

b,信號換層時(shí),最好不要改變參考層的網(wǎng)絡(luò )屬性。雖然參考層發(fā)生了改變,但如果同為GND或電源屬性,可利用附近的GND或電源的過(guò)孔實(shí)現返回路徑的通路(這個(gè)也正是說(shuō)明了換層處加地孔的原因)雖然這個(gè)過(guò)程發(fā)生了阻抗的變化,但由于過(guò)孔的尺寸較小,容性、感性寄生部分較低,過(guò)孔本身產(chǎn)生的阻抗變化可以忽略,因此對返回路徑的影響不大。如果網(wǎng)絡(luò )屬性發(fā)生了改變,,返回路徑就只能借助平面耦合電容或單板上的電源耦合電容,且兩參考層之間存在層間阻抗。同時(shí)會(huì )不可避免的產(chǎn)生一些壓降,信號發(fā)生畸變。

注意:在信號過(guò)孔附近增加的同屬性的過(guò)孔,一般要求該過(guò)孔與信號過(guò)孔的距離不要太遠,50mil以?xún)仁潜容^合適的。同時(shí)當很多信號換層時(shí),主要添加多一些過(guò)孔,這些過(guò)孔同時(shí)不應太近,避免信號回路上產(chǎn)生串擾。

c,如果換層前后兩參考層網(wǎng)絡(luò )屬性不同,那就只能盡量要求兩參考層相距較近,以減少層間阻抗和返回路徑上的壓降了。

對于設計者來(lái)說(shuō),當然是以不跨分割,不換層為最好的。