【導讀】想知道有幾哪種芯片測試方法嗎?混合測試法又有哪些優(yōu)點(diǎn)?請看本文Mentor Graphics 近日發(fā)布一份題為《汽車(chē)如何推動(dòng)新的可測性設計(DFT)技術(shù)》的研究報告。

《汽車(chē)如何推動(dòng)新的可測性設計(DFT)技術(shù)》的中文版研究報告全文可在 Mentor Graphics 的官方網(wǎng)站閱讀和下載: http://mentorg.com.cn/aboutus/view.php?id=256 。

背景介紹

隨著(zhù)人們對安全關(guān)鍵應用設備,尤其是汽車(chē) IC(集成電路),提出了新的需求,DFT(可測性設計)技術(shù)又再次受到重視。越來(lái)越多的處理器被運用于汽車(chē)的剎車(chē)系統、發(fā)動(dòng)機控制、平視顯示器、導航系統和圖像傳感器等等。這些芯片必須滿(mǎn)足非常高的質(zhì)量和可靠性標準,所以芯片制造商也必須進(jìn)行高水平的生產(chǎn)測試和系統內部測試。不僅如此,他們還必須在盡可能提升測試水平的同時(shí),確保測試時(shí)間和成本不會(huì )增加。

全文要點(diǎn)與大綱如下:

●幾種芯片測試方法

如今有兩種測試方法被眾多安全關(guān)鍵設備開(kāi)發(fā)商迅速采納 -- 單元識別 (Cell-Aware) 自動(dòng)測試向量生成 (ATPG) 法和 ATPG/邏輯內建自測試 (LBIST) 綜合運用法。單元識別測試法可實(shí)現每百萬(wàn)缺陷數 (DPM) 為零的目標。綜合測試法則通過(guò)將ATPG和LBIST 邏輯電路測試法相結合來(lái)提高測試質(zhì)量和效率。

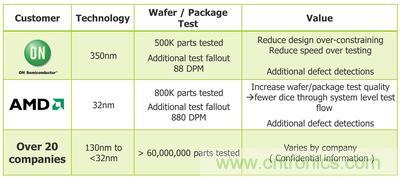

事實(shí)證明,單元識別 ATPG 測試法是唯一可以發(fā)現傳統方法檢測不出的缺陷的方法。它可以發(fā)現一套完整的針對固定故障、節點(diǎn)跳變和時(shí)延缺陷的測試方法發(fā)現不了的缺陷,因為這種方法首先就對標準單元進(jìn)行物理布局時(shí)可能出現的實(shí)際缺陷進(jìn)行模擬。在新技術(shù)的改進(jìn)下,單元識別測試法中的測試向量大小得以縮小,但整個(gè)測試向量仍大于傳統的測試方法產(chǎn)生的測試向量,因此要進(jìn)行嵌入式壓縮。許多公司因為采用單元識別測試法而收效顯著(zhù)。部分成效的概述請見(jiàn)圖1。

圖1:截至2013年12月來(lái)自使用單元識別測試法的公司的硅結果。安森美半導體 (On Semiconductor) 結果在2013年 ETS 上進(jìn)行了發(fā)布;AMD 結果在2012年 ITS 上進(jìn)行了發(fā)布。

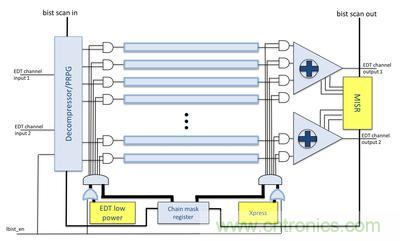

越來(lái)越多的客戶(hù)在設計相同的電路時(shí)同時(shí)采用嵌入式壓縮和 LBIST 測試法。由于這兩種技術(shù)能夠以類(lèi)似的方式運用掃描鏈,因此可以將兩者整合成可共享的統一邏輯,從而幫助客戶(hù)更有效地運用這種方法。綜合測試邏輯架構請見(jiàn)圖2。

圖2:混合壓縮邏輯架構和邏輯內建自測試共享大部分解壓?jiǎn)卧?LFSR 和壓縮單元/MSIR 邏輯。

嵌入式壓縮解壓?jiǎn)卧谠O計上也可整合進(jìn)線(xiàn)性反饋移位寄存器 (LFSR),為邏輯內建自測試帶來(lái)偽隨機模式。邏輯內建自測試和嵌入式壓縮邏輯都可通過(guò)相移位器為掃描鏈提供數據,這樣邏輯得以完全共享。掃描鏈結果通過(guò)嵌入式壓縮擠壓到一起。該邏輯主要與邏輯內建自測試混合使用,減少進(jìn)入一個(gè)簽名計算器的掃描鏈結果數量。與單獨進(jìn)行嵌入式壓縮和邏輯內建自測試相比,該共享邏輯可讓控制器尺寸縮小20%至30%。

●混合測試法的優(yōu)點(diǎn)

混合使用嵌入式壓縮和邏輯內建自測試的一大好處便是雙方互補。例如,嵌入式壓縮可實(shí)現非常高品質(zhì)的生產(chǎn)測試。這意味著(zhù)您需要較少的邏輯內建自測試點(diǎn)就可以提高隨機抵抗性邏輯的可測性,這可縮小邏輯內建自測試點(diǎn)的面積。相反地,X-bounding 以及任何為邏輯內建自測試增加的測試點(diǎn)都可提高電路的可測性,并改善嵌入式壓縮覆蓋和模式計數結果。

汽車(chē)電子是半導體行業(yè)增長(cháng)最迅速的領(lǐng)域之一,這些安全關(guān)鍵型設備標準正推動(dòng)新DFT技術(shù)的出現。嵌入式壓縮的發(fā)明是重要的測試進(jìn)步。

報告作者簡(jiǎn)介

Ron Press 是明導硅測試解決方案產(chǎn)品的技術(shù)營(yíng)銷(xiāo)經(jīng)理。他在測試和 DFT(可測性設計)行業(yè)有著(zhù)25年的經(jīng)驗,曾多次出席全球各地的 DFT 和測試研討會(huì )。他發(fā)表了數十篇與測試相關(guān)的論文,是國際測試會(huì )議 (ITC) 指導委員會(huì )的成員、IEEE 計算機學(xué)會(huì ) (IEEE Computer Society) 的 Golden Core 成員以及 IEEE 的高級會(huì )員。Press 擁有多項減少引腳數測試和無(wú)毛刺的自由時(shí)鐘切換的專(zhuān)利,并正在申請3D DFT 專(zhuān)利。